复旦微ZYNQ SOC AXI_DMA数据传输

国产复旦微SOC平台的应用尚未普及,在ARM CONTEX A7+FPGA架构(PS+PL架构)中,CPU与FPGA通过AXI总线协议进行数据传输,小批量数据可以通过AXI_lite进行交互,大容量的数据需要采AXI_stream协议。

一,AXI总线简介

复旦微采用四核APU,GP总线接口和HP总线接口带宽支持64位。AXI_DMA可将在数据搬运工作中不占CPU资源,为内存AXI4_Stream外设之间提供高带宽的直接存储访问,大大提高数据传输效率。AXI协议提供单一的接口定义,能用在下述三种接口之间:master/interconnect、slave/interconnect、master/slave。在AXI总线使用过程中可以使用共享地址与数据总线,共享地址总线,多数据总线,multilayer多层,多地址总线,多数据总线。在大多数系统中,地址通道的带宽要求没有数据通道高,因此可以使用共享地址总线,多数据总线结构来对系统性能和互联复杂度进行平衡。AXI所采用的是一种READY,VALID握手通信机制,即主从模块进行数据通信前,新根据操作对各所用到的数据、地址通道进行握手。主要操作包括传输发送者A等到传输接受者B的READY信号后,A将数据与VALID信号同时发送给B。

二,AXI_DMA:包含四部分

1,数据模块用来实现存储器接口和流接口的转换。

2,Scatter/Gather模块用来实现设置DMA对非连续内存访问的支持;状态寄存器主要用来寄存DMA的工作状态等信息,用户可通过 AXI GP接口读取这些状态信息;配置寄存器模块主要用来对AXI_DMA通过GP接口进行初始化的配置以使其能正常工作。

3, Direct Register Mode具备DMA的基本功能,给出源(目的)地址和传输长度之后就可以开启一次传输。配置完一次寄存器之后只能完成存储器连续地址空间的读写,在此模式下发送数据为MM2S_LENGTH寄存器所填写的长度。

4,当发送数据大于收数据时会产生中断,中断处理函数中读取状态寄存器错误提示S2MM_DMASR[DMAIntErr],此错误正好是填写的收数据缓冲空间小于需要收的数据空间(自环下为发空间)。读取内存数据查看实际已经传输了填写的收数据空间的数据。当发送数据小于收数据时会产生中断,读取S2MM_LENGTH寄存器,收取数据为发送数据长度,收数据中断由tlast信号触发,表示收数据完成,软件可以读取S2MM_LENGTH寄存器查看真实收到的数据包大小。

三,AXI_DMA驱动

1,AXI_DMA驱动软件实现:数据发送模块用来将数据从PS 搬迁到PL,数据接收模块负责将PL数据搬迁到PS。收发数据在大体流程上基本一致,最大的差别在于通道的申请上,收发数据需要申请两个相对独立的DMA通道,填写收发地址和回调函数注册时也需要对应到相应通道上去。

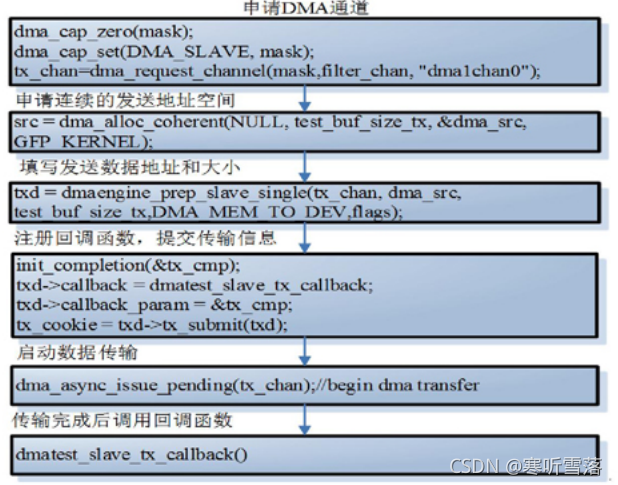

2,AXI_DMA 驱动发送数据流程

3,PS控制AXI_DMA: PS采用内存映射的方式将外设的寄存器映射进PS的内存空间,可采用指针操作的方式对外设的寄存器进行访问。

4, 设备树修改:FMQL设备树关于DMA部分修改PS中断号为25、26。

5, PL搭建与LINUX系统文件制作:选择AXI_DMA IP CORE,搭建FPGA BD工程,短接收发通道,加入ILA监测信号。编译生成BIT、HDF文件。通过FMQL开发环境PROCISE解析PL配置,生成设备树源文件夹、FSBL工程,IAR编译生成flsb.out用于第一阶段启动配置。由复旦微提供的BSP包编译生成u-boot.、内核镜像、设备树、根文件系统。由PROCISE工具打包生成BOOT.bin。

四, 传输结果

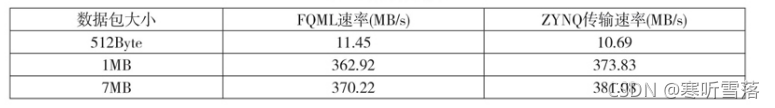

1,测试:PS应用测试程序下发不同大小的数据包,通过PL侧回环,PS读数据通道将AXI_DMA数据取回效验。国产复旦微FMQL系列芯片PS与PL数据交互性能不亚于ZYNQ 7000系列,在时钟频率100MHZ和总线位宽为32位的情况下,实测PS与PL数据传输传输速率最高可达370MB/s左右。增加总线位宽、时钟频率、突发长度可以得到更高的传输速率。AXI_DMA传输速率随着帧长增加而增加,适用于大包数据传输。

2,xilinx和fmql AXI总线速度对比

本文来自互联网用户投稿,文章观点仅代表作者本人,不代表本站立场,不承担相关法律责任。如若转载,请注明出处。 如若内容造成侵权/违法违规/事实不符,请点击【内容举报】进行投诉反馈!