计算机组成原理实验logisim(四)之运算器实验

保姆级实验图

超多图预警!

超超多图预警!!

超超超多图预警!!!

关于实验部分:

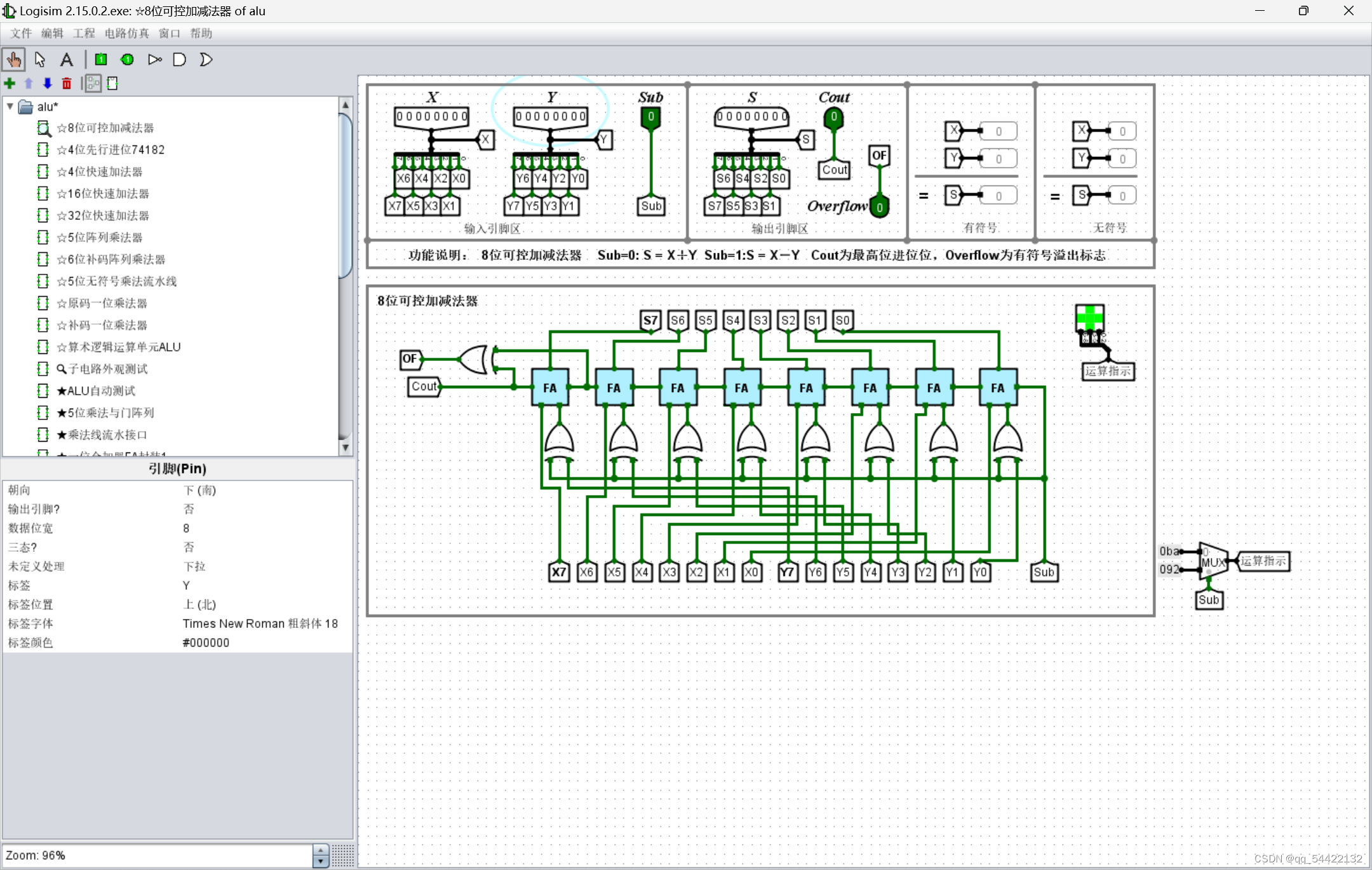

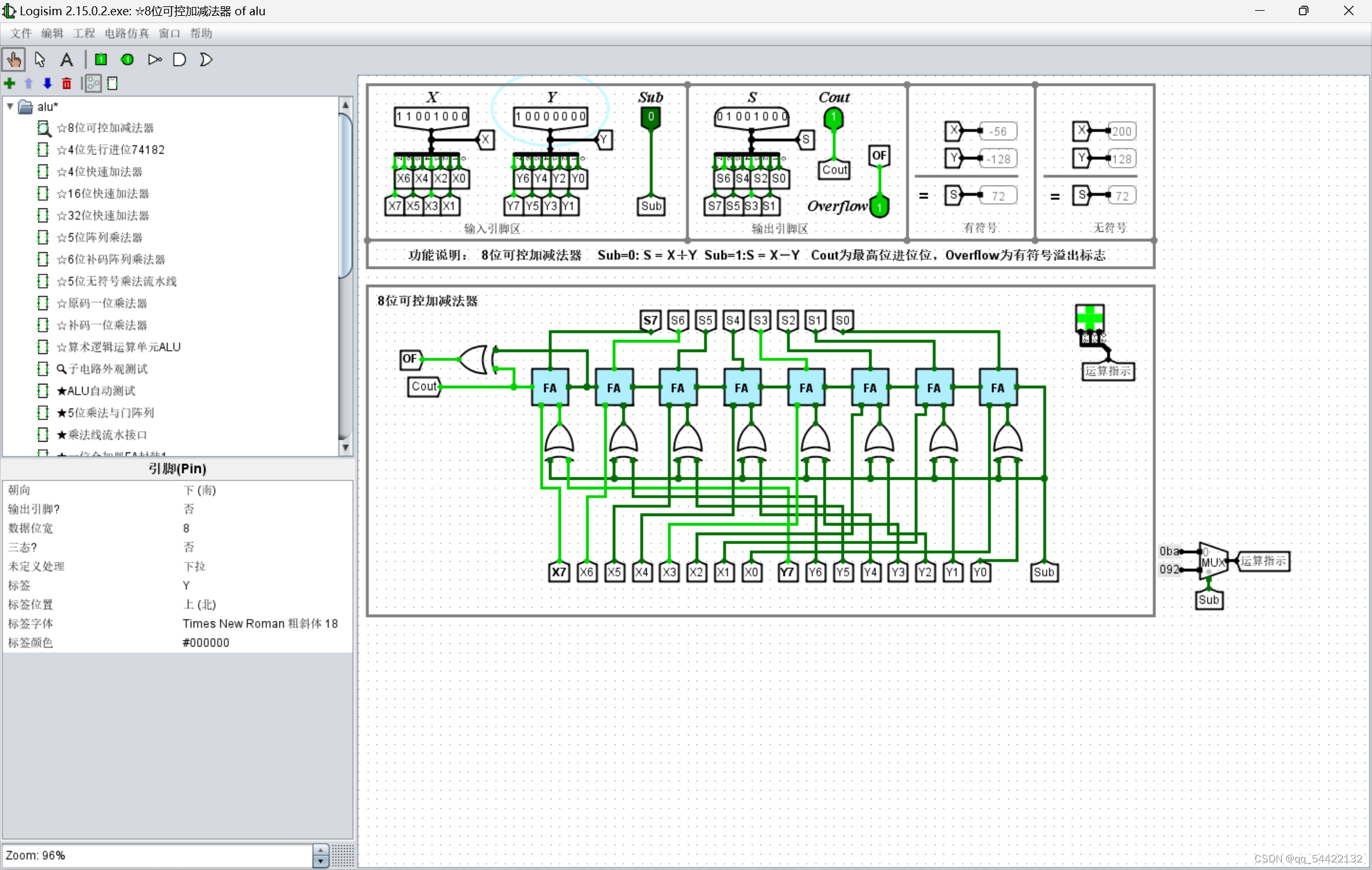

(1)8位可控加减法器:

直接连图如下,可先拖入器械再进行连线。开始连线时直接连即可,不需要格外注意位宽的改变。因为所有位宽都是1

(为何我的图相比起于教程看起来如此复杂?!请格外注意最下面一排tunnel的排列!!关于各部件的排列顺序我几乎是原封不动)

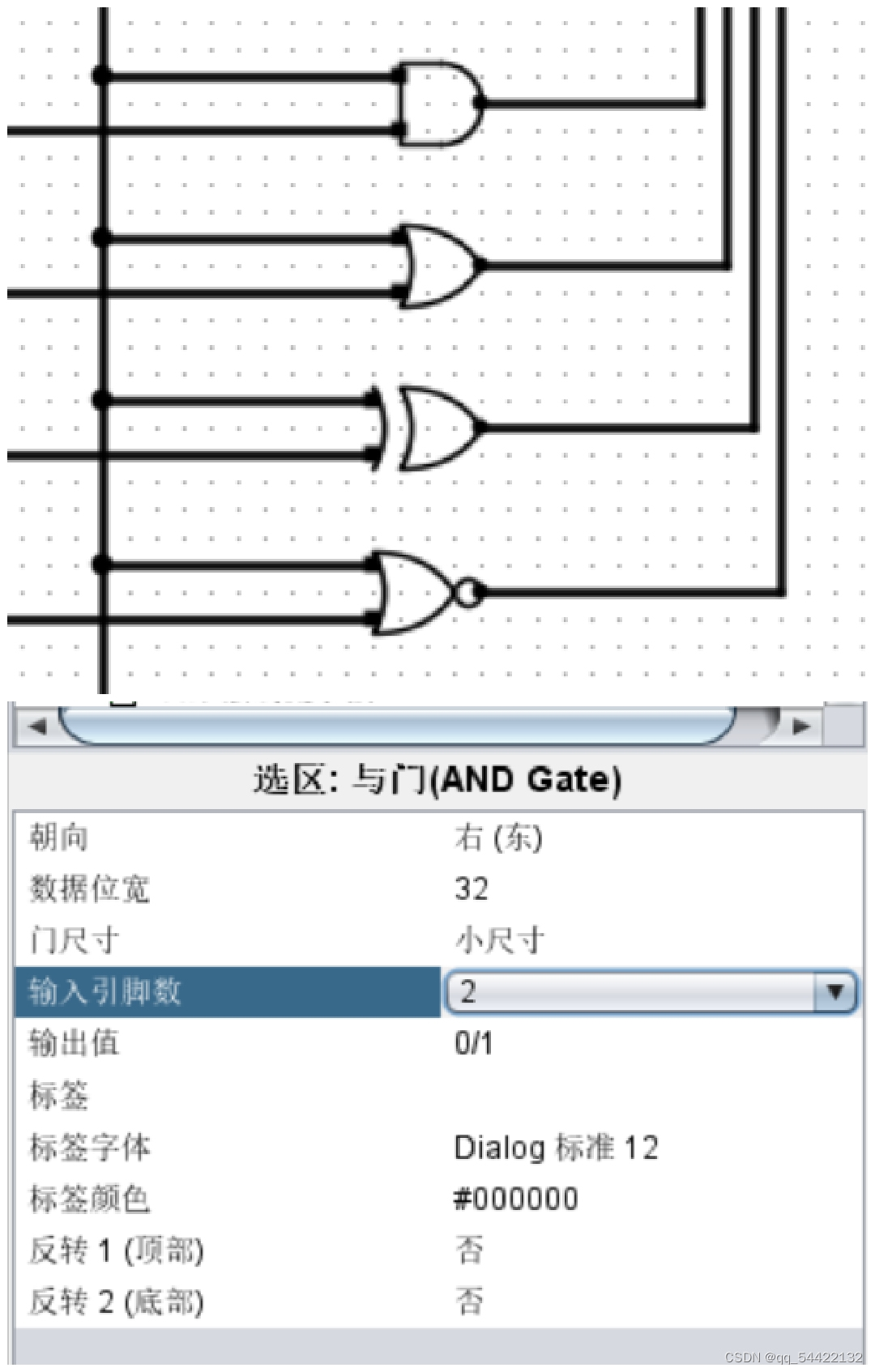

(2)4位先行速位74182:

连图如下,需要在连线之前格外注意“或门”和“与门”的位宽,将16改为1,不然数据无法通行

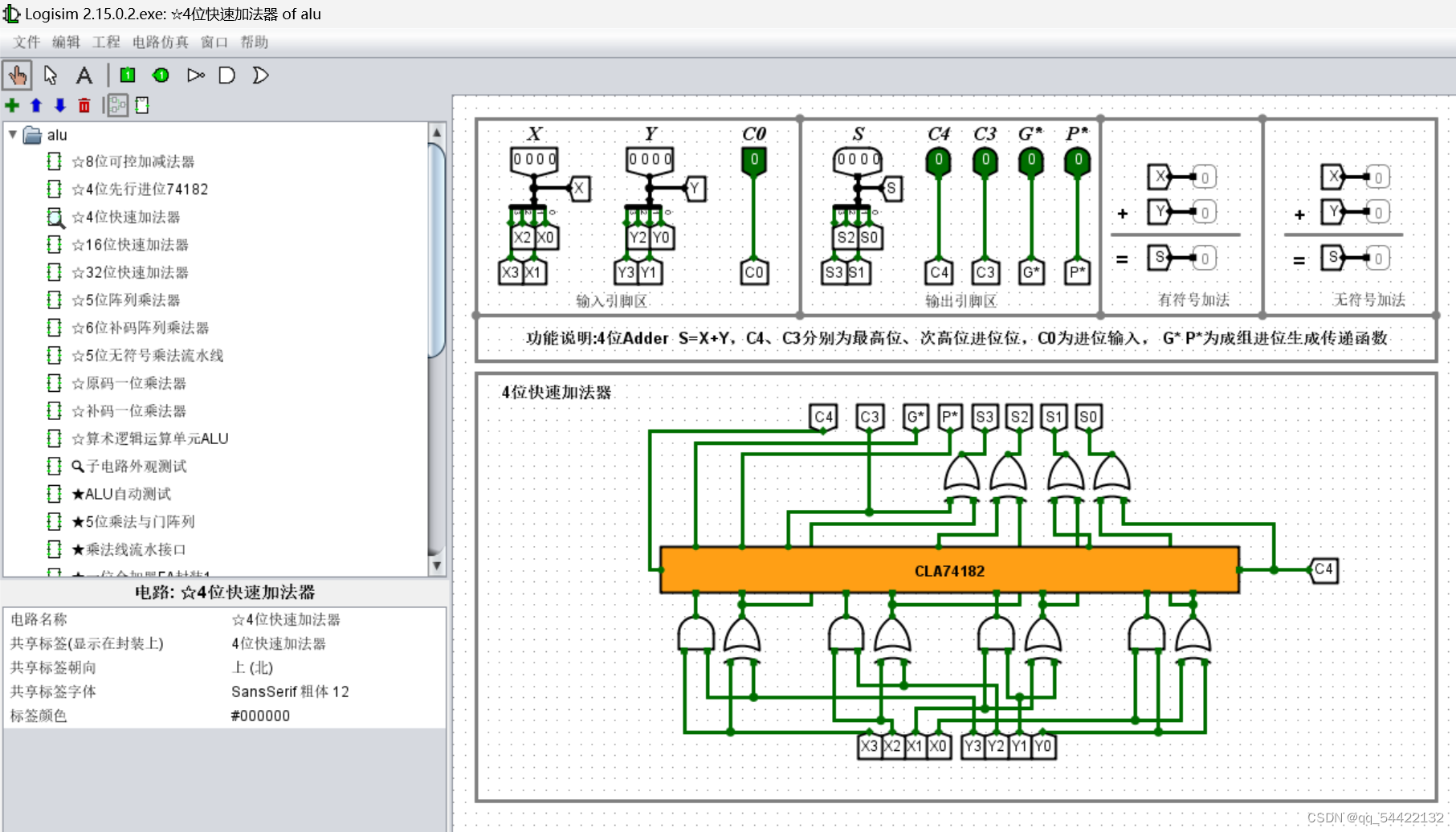

(3)4位快速加法器

连图如下,需要在连线之前格外注意“异或门”和“与门”的位宽,将16改为1,不然数据无法通行。此外,“4位先行进位”背后有部分被挡住的连线,需注意

(为何我的图相比起于教程看起来如此复杂?!请格外注意最下面一排tunnel的排列!!关于各部件的排列顺序我几乎是原封不动)

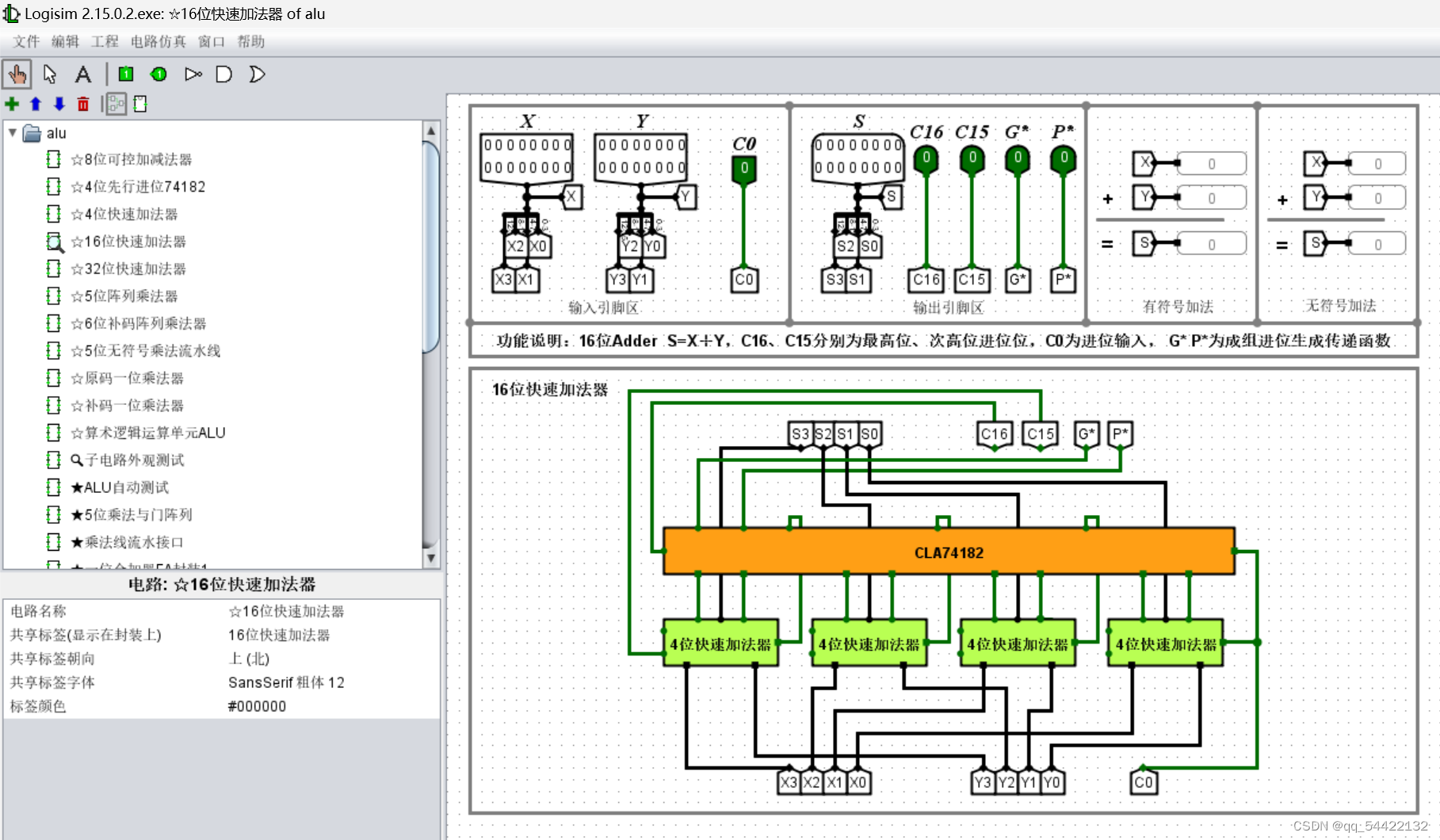

(4)16位快速加法器

连图如下,无特别需要注意的地方

(为何我的图相比起于教程看起来如此复杂?!请格外注意最下面一排tunnel的排列!!关于各部件的排列顺序我几乎是原封不动)

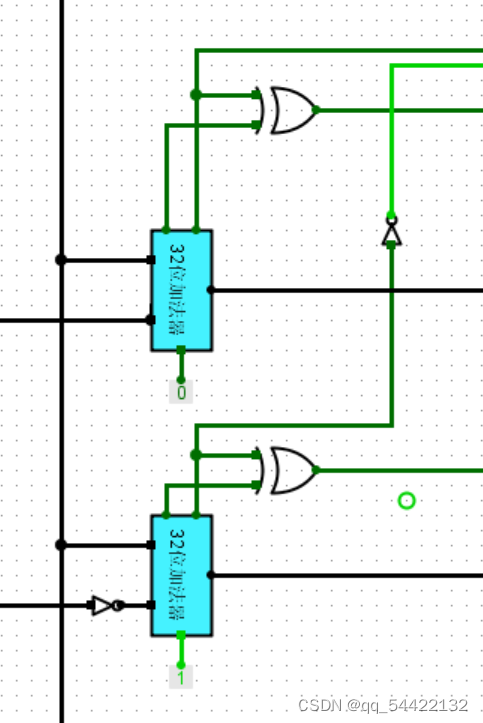

(5)32位快速加法器

连图如下,直接连线即可。但需注意由于“4位快速加法器”的存在,使得该物件可以通行1位和4位位宽的数据,因为不需专门修改下方输出隧道的位宽

(为何我的图相比起于教程看起来如此复杂?!请格外注意最下面一排tunnel的排列!!关于各部件的排列顺序我几乎是原封不动)

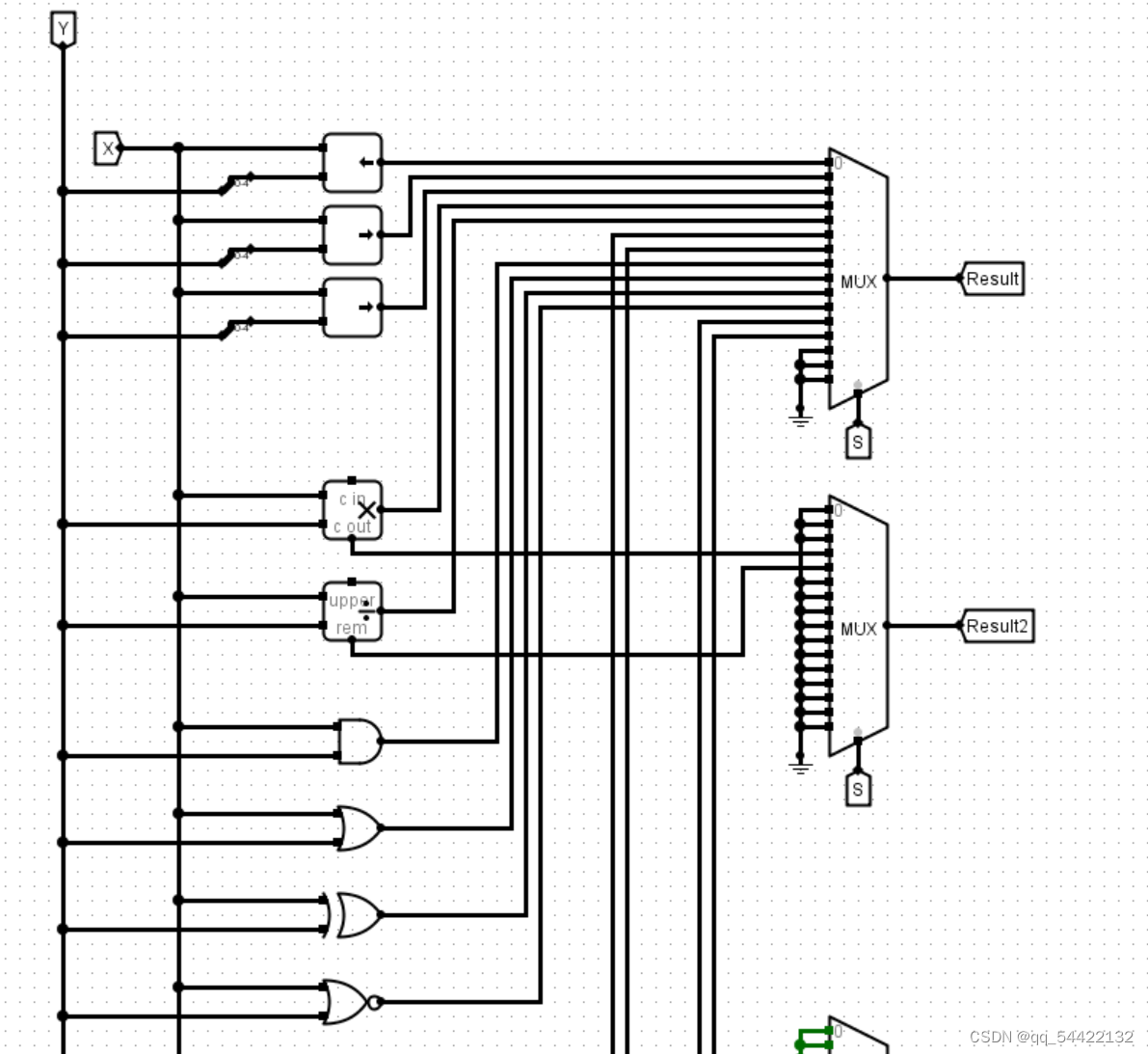

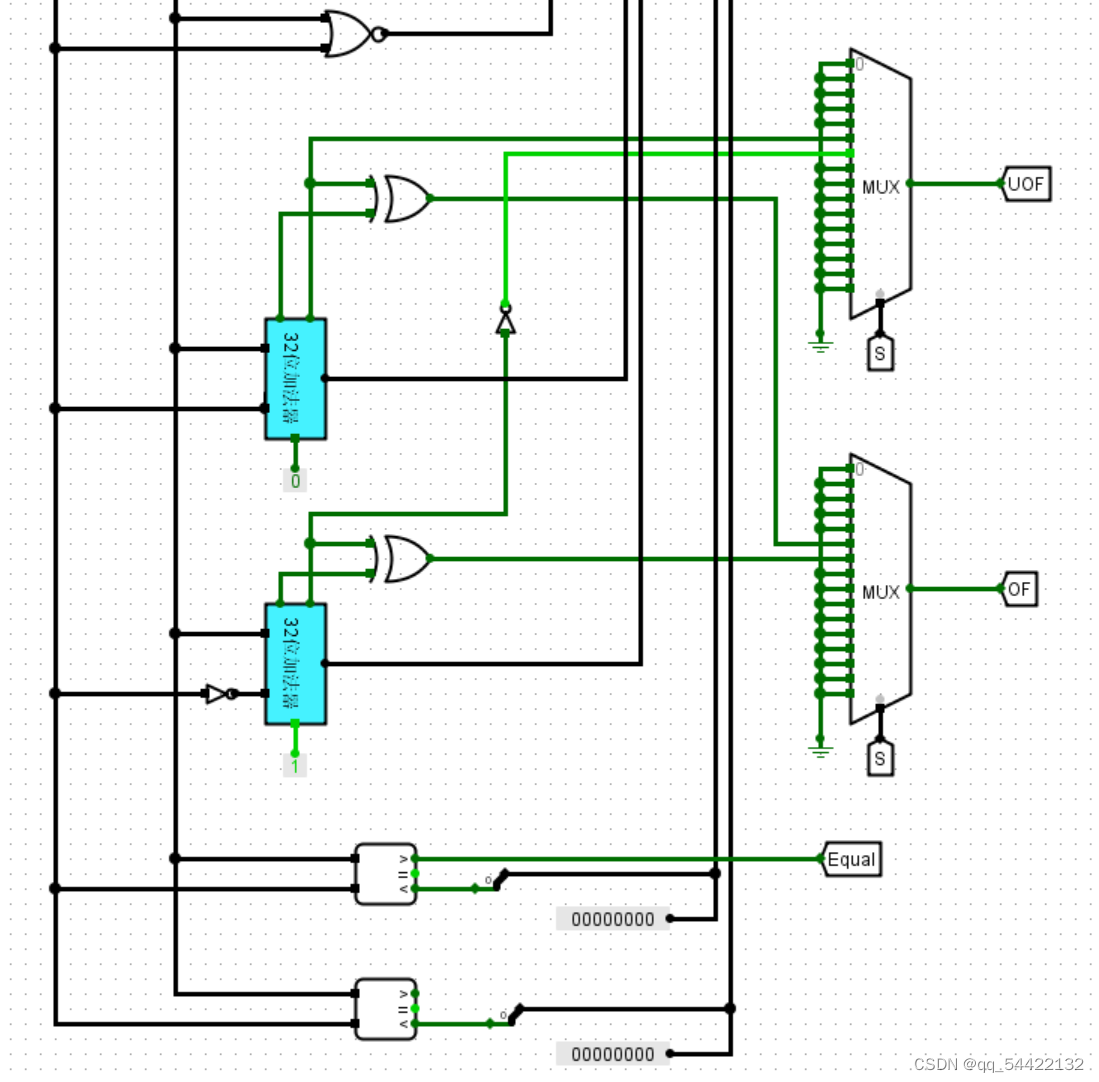

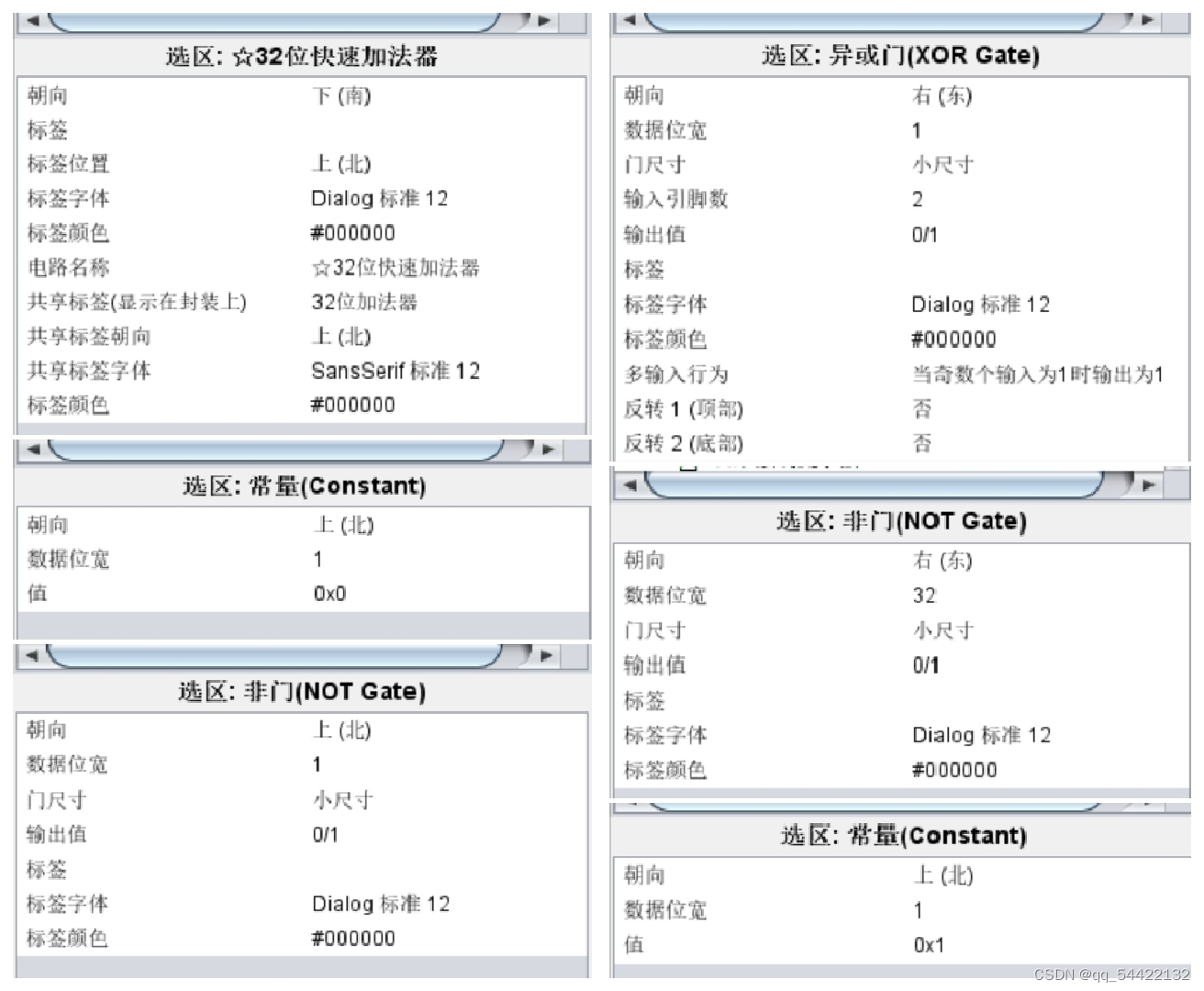

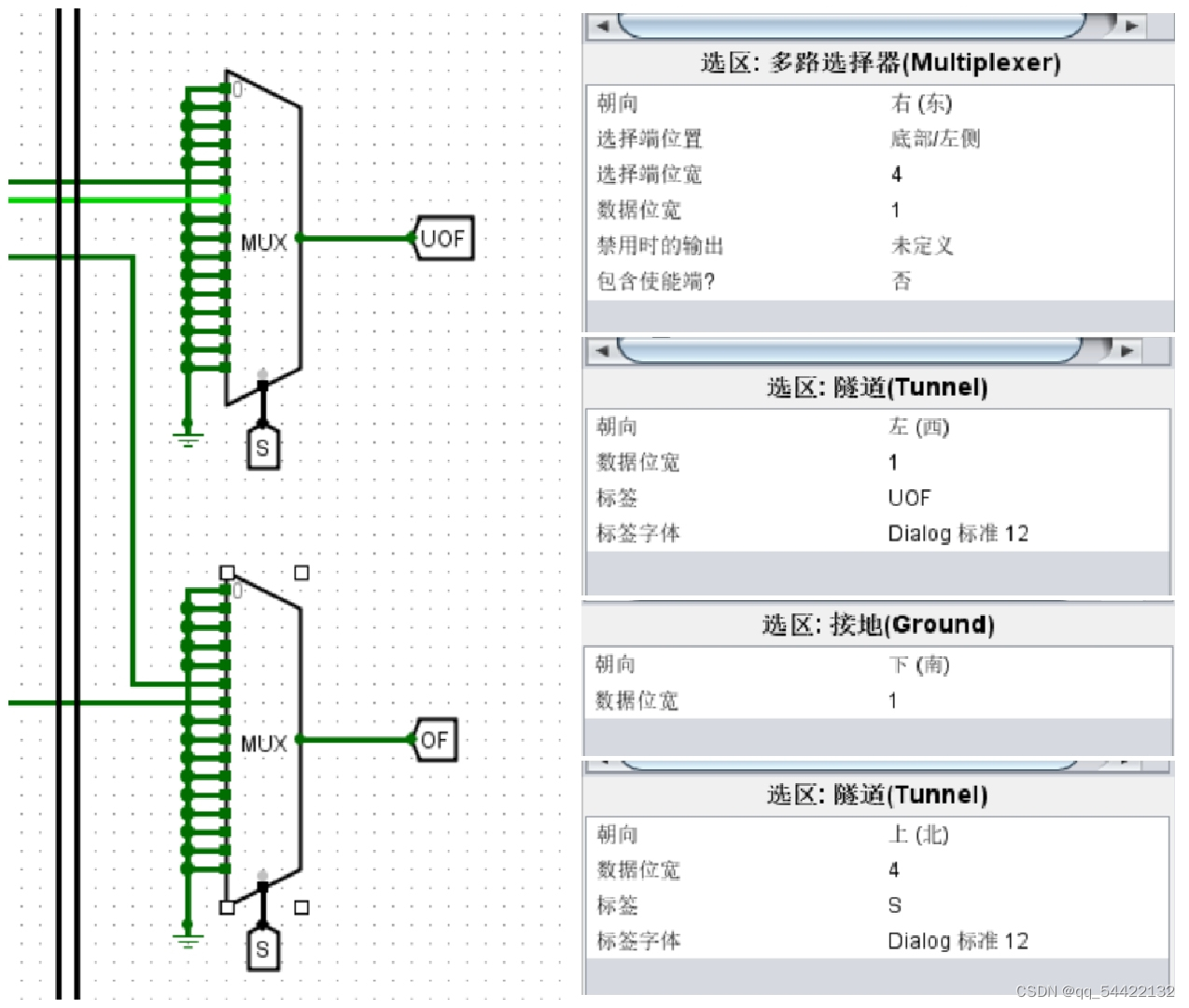

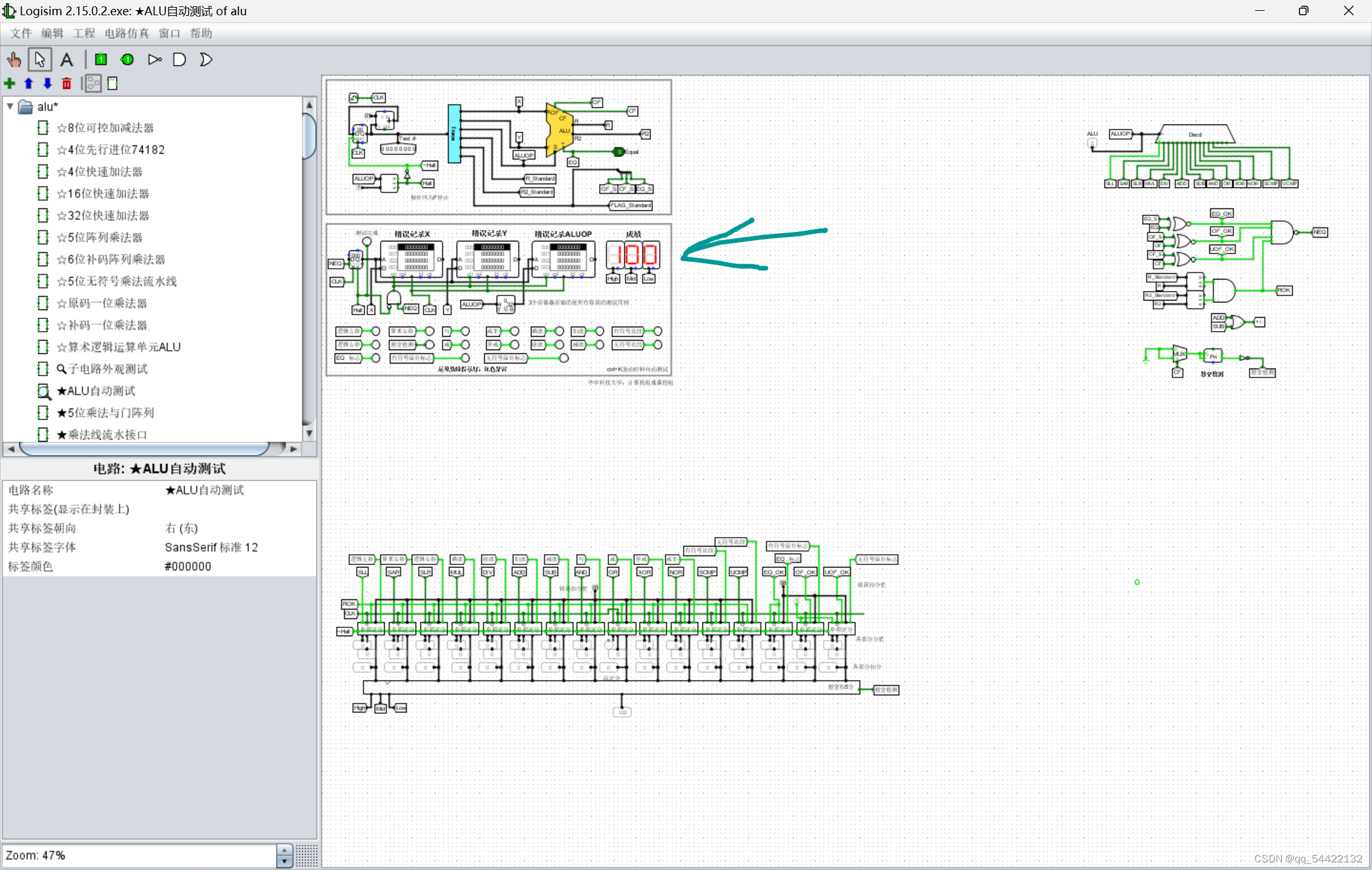

(6)算术逻辑运算单元ALU:利用alu.circ文件中已有的“★ALU自动测试”电路进行测试。

放入器件如图,并连线。

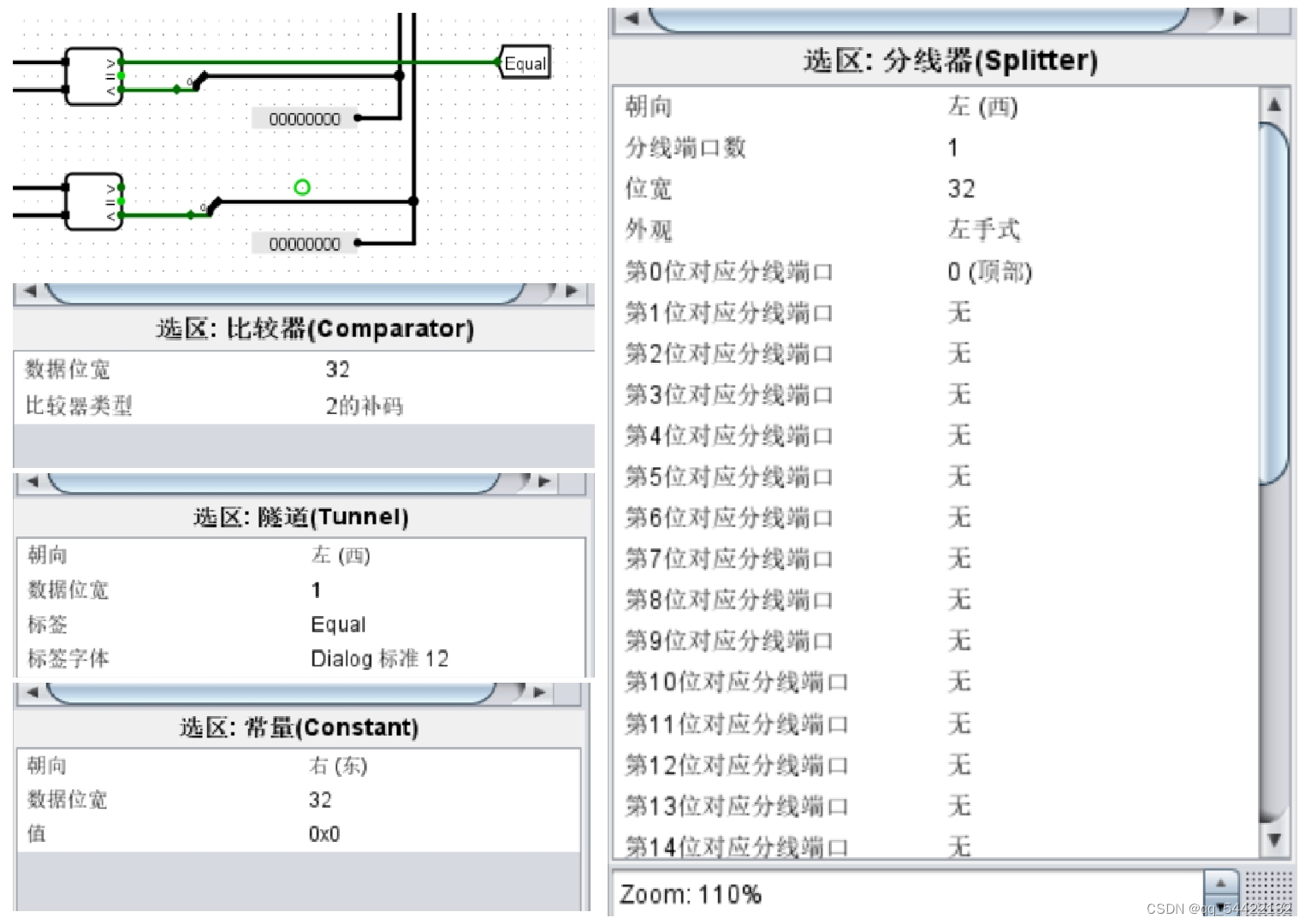

注意,上半张图中所有连入32位宽多路选择器的器件和的“数据位宽”都是32,而中间部分连入1位多路选择器的器件的“数据位宽”皆为1(除了连向“32位加法器”的那一个非门,是32位)。除此之外,与“比较器”相连的器件除了“Equal隧道”都是32的数据位宽。

还要注意第二个与“32位加法器”相连的“常量”要将其“值”改为“0x1”

至于为何上下两部分的位宽不一致,原因同第五个小实验

稍微细节一点的图(各部件大家该看得够清楚了吧):

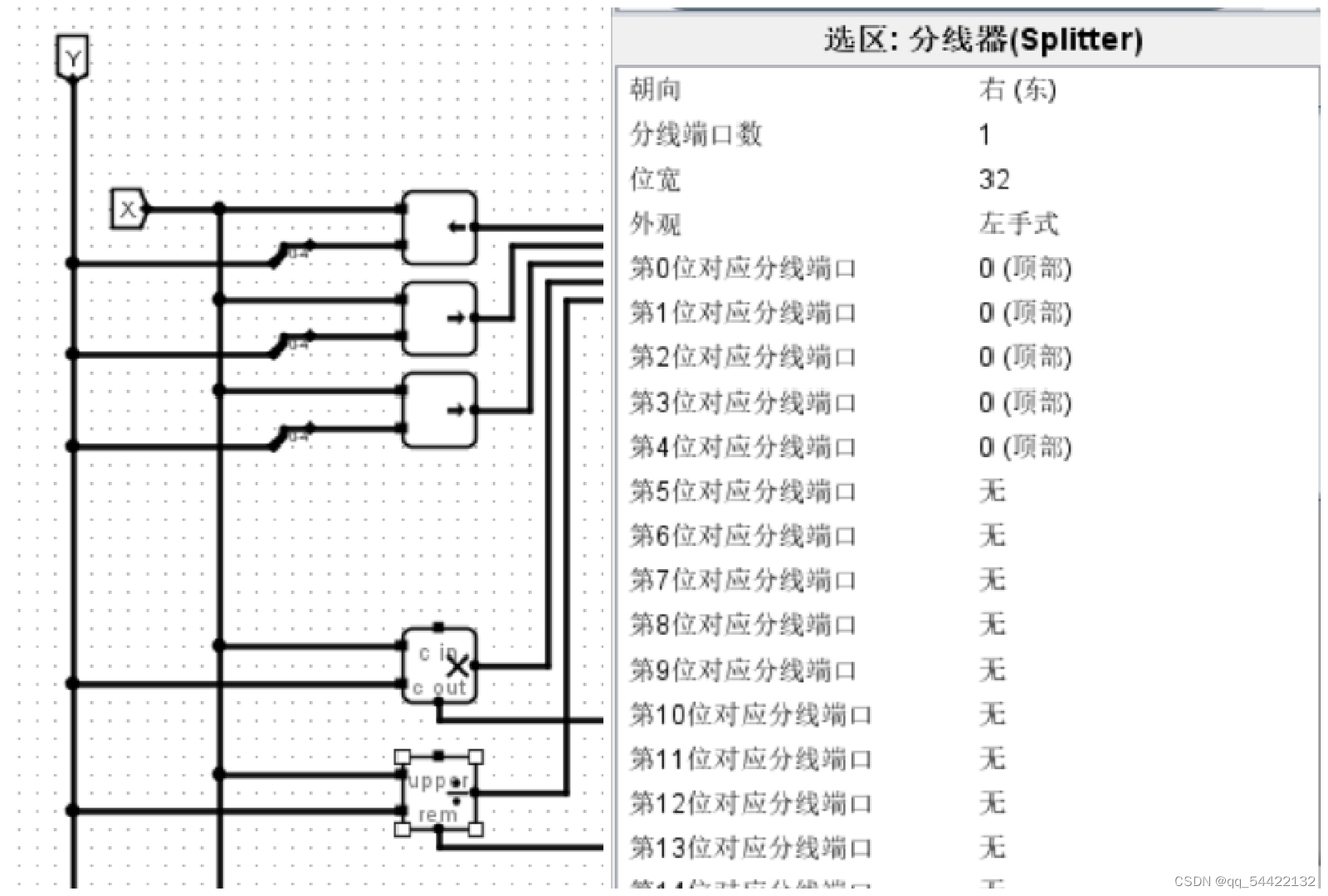

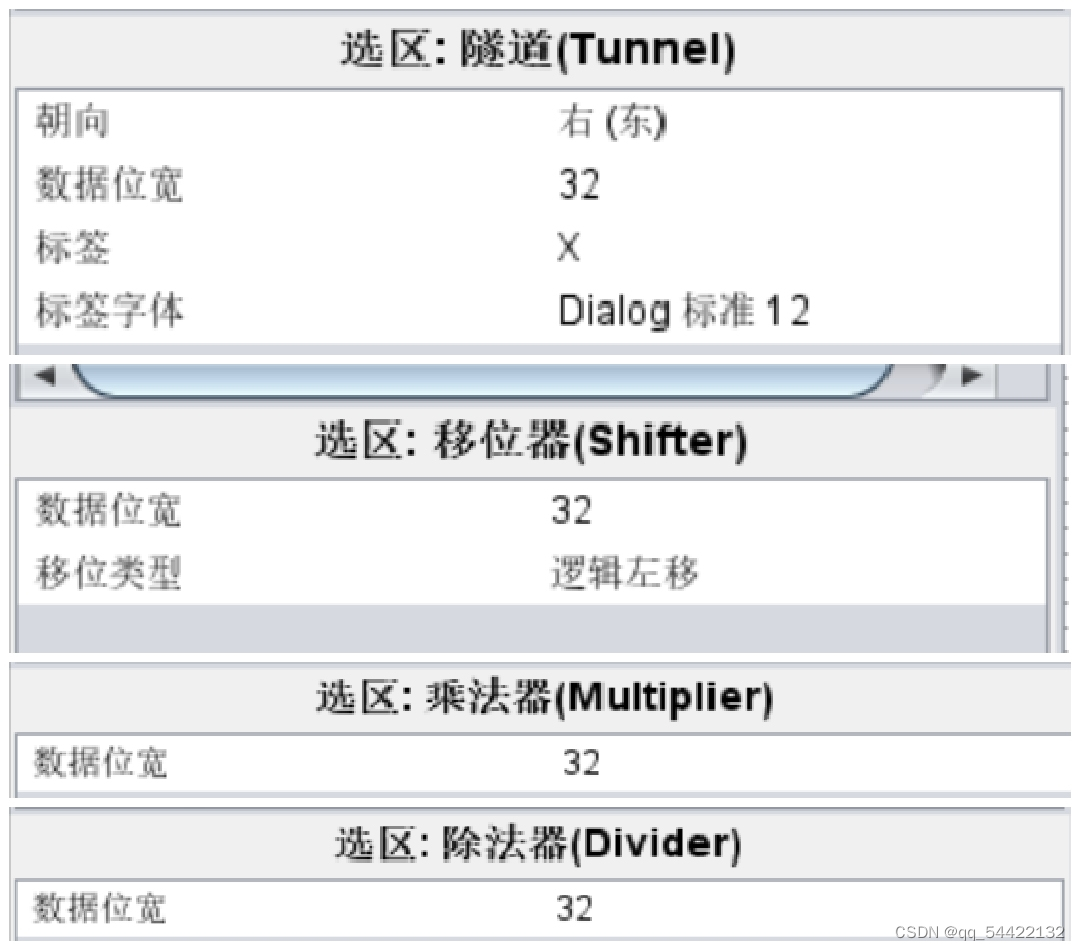

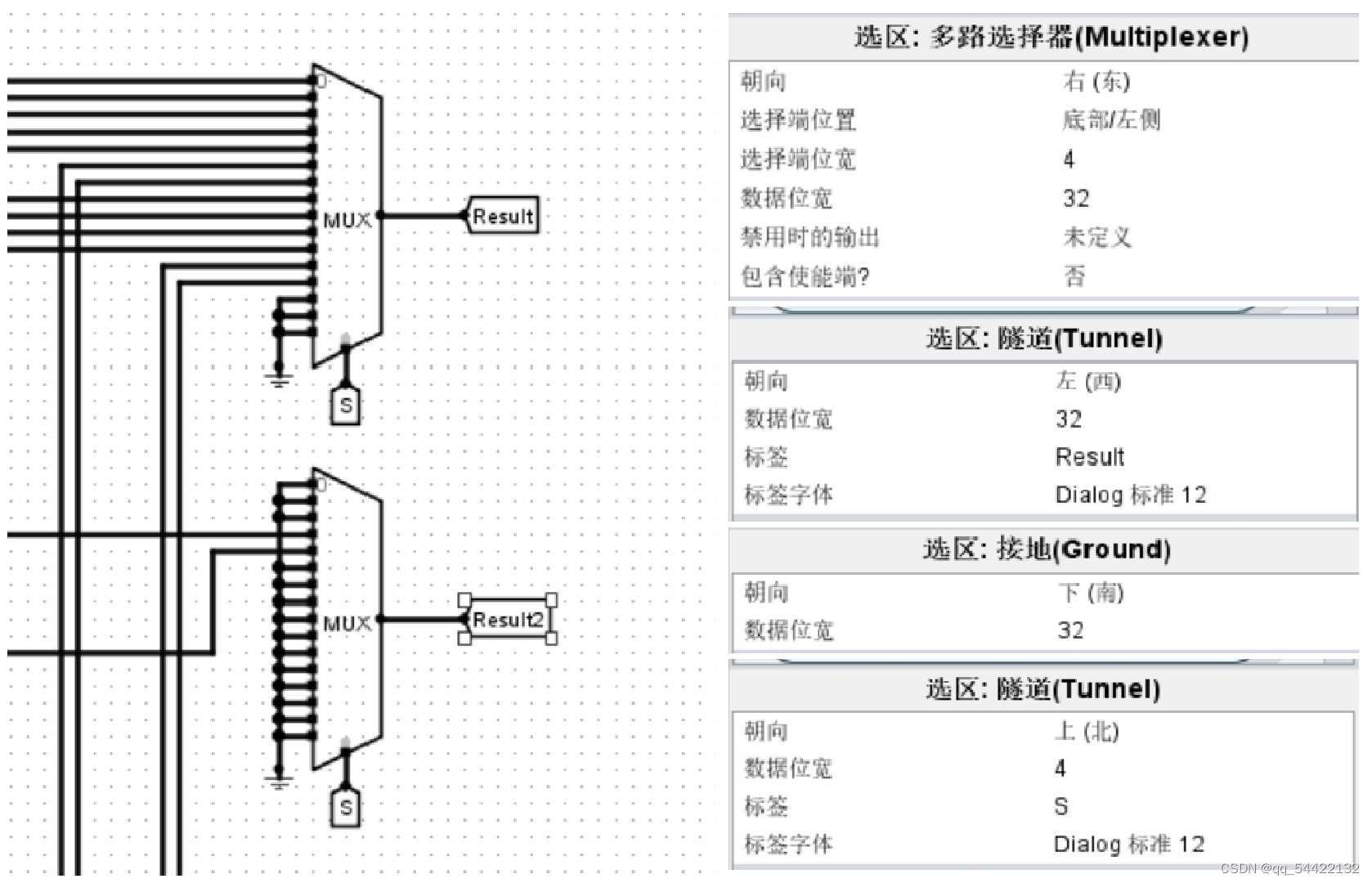

然后是更细节的图(关于各部件的具体参数,没截完整图的部分就表示其余项没有修改过):

板块一:

板块二:(上面两个MUX,接地线,各tunnel的参数都一致)

板块三:(与门,或门,异或门,或非门参数一样)

板块四:(两个异或门参数一致,两个常量以及两个非门参数不一致)

板块五:(下两个MUX系数一致)

板块六:

就问详不详细

关于学术问题,为何这样连什么的,就别问我了,我也没有搞的那么透彻

然后关于测试部分

第一个实验就是加法器、减法器的实验。

当“Sub”为0时,该组件为一个加法器,点击改变X,Y的数值(0或1),使得结果得到改变

当“Sub”为1时,该组件为一个减法器,点击改变X,Y的数值(0或1),使得结果得到改变

其中,“Cout”来判定无符号溢出,“Overflow”来判定有符号溢出(举例如下图)

第二到第五个实验的测试,具体怎么测试好吧我也不太清楚,听室友说就是让你分析各种亮灯的原理,比如你点这个,那个为什么颜色要变等等,我就不粘图了,恩大家加油

最后一个实验测试结果 就是当你把图连好后,“ALU自动测试”的“成绩”那儿的数字会从95变成100

本文来自互联网用户投稿,文章观点仅代表作者本人,不代表本站立场,不承担相关法律责任。如若转载,请注明出处。 如若内容造成侵权/违法违规/事实不符,请点击【内容举报】进行投诉反馈!