数字音频接口—TDM总线协议

一 TDM概述

音频TDM(Time-Division Multiplexing)协议是一种用于将多个音频信号合并为一个信号的通信协议。它通过将多个音频信号按时间切片,将它们组合成一个连续的数字流,从而实现同时传输多个音频信号,当前被广泛应用于智能座舱音频领域。

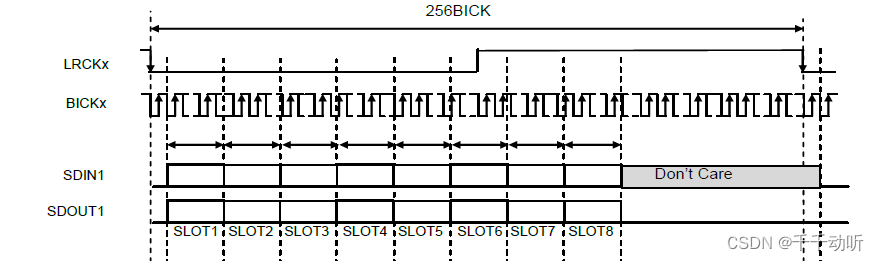

图1 TDM数据传输示意图

如图1 TDM数据传输示意图。 每个音频信号都被分配一个固定的slot(时间槽),这些slot按顺序排列组成一个帧。每个slot的长度相等且固定,可以容纳一个音频信号的数据。通过按照事先约定的顺序轮流填充每个slot,多个音频信号的数据被交错传输。

在发送端,音频TDM协议将多个音频信号的样本值分别放置在对应的slot中。

在接收端,协议按照相同的顺序将slot的数据取出,并重新还原成原始的音频信号。通过这种方式,多个音频信号可以同时传输在同一个信道上,实现了信道资源的高效利用。

注意:上面提到的slot与音频的声道没有直接的对应关系,跟实际芯片平台和Codec定义有关,不能简单的讲slot1理解位音频数据的第一个声道。例如假设slot1的长度位32bit时,slot1可以传输两路16位的音频数据。这种灵活性允许在不同的TDM实现中,根据具体的需求和约定来确定时间槽的长度以及每个时间槽所承载的音频信号的格式。

二 TDM信号定义

音频TDM通过使用BLCK作为位时钟信号来确定数据传输的时钟速率和时序。Frame Sync信号用于标识音频帧的开始和结束,确保正确地组合和解析音频数据。Data IN和Data OUT信号引脚用于输入和输出音频数据,实现多路音频信号的合并和传输。

BLCK(Bit Clock):BLCK引脚是音频TDM中的时钟信号引脚。在每个BLCK时钟周期内,只能传输一个数据位。BLCK信号的频率决定了数据传输的速率,每个数据位在一个时钟周期内进行传输。发送端在每个时间槽中依次填充数据位,并在每个BLCK时钟周期根据BLCK信号的边沿将数据位传输出去。接收端根据BLCK信号的时钟边沿来采样和解析数据位,以还原音频信号。

Frame Sync(帧同步):Frame Sync引脚用于标识数据帧的开始和结束。在音频TDM中,多个slot被组合成一个完整的音频帧。Frame Sync信号的状态变化指示一个新的音频帧的开始。接收端根据Frame Sync信号来识别和解析每个slot的数据,并将其组合成原始的音频信号。

SD IN引脚:SD IN引脚是用于输入音频数据的引脚。

SD OUT引脚:SD OUT引脚是用于输出音频数据的引脚。

| I2S | TDM | |

| 位时钟 | BLCK | BLCK |

| 同步信号 | WS (左右声道) | Frame Sync(帧同步) |

| 数据输入 | SD IN | SD IN |

| 数据输出 | SD OUT | SD Out |

在I2S中,通过WS引脚来区分左右声道,每个样本由左右声道交替传输。而在TDM中,通过Frame Sync信号来标识音频帧的开始和结束,一个音频帧可以包含多个slot。

三 主从模式

TDM传输两种基本的模式:主模式(Master Mode)和从模式(Slave Mode)。

3.1 主模式(Master Mode)

在主模式下,一个设备被配置为主设备或主时钟源。主设备负责生成时钟信号,并控制整个TDM传输的时序。它确定了传输的速率、通道顺序和帧结构。其他设备在从模式下进行传输,并按照主设备的时钟信号进行同步。主模式适用于控制整个TDM系统的主要设备。

3.2 从模式(Slave Mode)

在从模式下,设备被配置为从设备或从时钟源。从设备接收主设备发送的时钟信号,并根据该时钟信号进行数据传输。从模式下的设备需要与主设备的时序保持同步,以确保数据的准确传输。从模式适用于与主设备进行协作的辅助设备。

四 TDM传输时序

目前并没有一个统一的标准来定义TDM传输的模式和时序,不同厂商对TDM传输的描述可能存在差异,但是会提供灵活的配置方法。在进行TDM传输配置时,需要仔细对照系统芯片(SoC)和外部CODEC的规格书来了解具体的配置要求。本文将以AKM CODEC芯片的规格书为例,大致介绍TDM传输的模式。

TDM协议的时钟速率等于采样率乘以TDM帧长。对于一个8slot、每个slot 32bit音频数据、采样率48kHz的系统,TDM的BCLK时钟速率为:8 × 32 × 48kHz = 12.288 MHz。在器件的Datasheet中,可以找到TDM128/TDM256/TDM384/TDM512等说法,这些数字表示单个TDM数据帧包含的数据比特数(即帧长)。例如,8 slot、32bit的音频数据也被称为TDM256(=8*32)。

4.1 Mode 0 I2S Compatiable Format

图2 TDM mode I2S Compatiable(TDM256)

如图2,这种传输模式的特点:

- 帧同步信号下降沿时表述一帧数据开始,低电平维持N/2 slot宽度,再变为高电平,直到下一帧数据开始又变低。

- 每帧数据开始传输时,有效数据延迟一个bit clock,即从帧同步信号开始后的第二BICK的上升沿才是第一个有效数据位。

4.2 Mode 1 MSB Justified Format

图3 TDM mode MSB Justified Format(TDM256)

如图3,这种传输模式的特点:

- 帧同步信号上降沿时表述一帧数据开始,高电平维持N/2 slot宽度,再变为低电平,直到下一帧数据开始又变高。

- 每帧数据开始传输时,有效数据位没有延迟,从左边对齐传输

4.3 Mode 2 LSB Justified Format

图4 TDM mode LSB Justified Format(TDM256)

如图4,这种传输模式的特点:

- 帧同步信号上降沿时表述一帧数据开始,高电平维持N/2 slot宽度再变为低电平,直到下一帧数据开始又变高。

- 每帧数据开始传输时,有效数据位没有延迟,从右边对齐传输

4.4 Mode 3 PCM Short Frame Format

图5 TDM mode PCM Short Frame(TDM256)

如图5,这种传输模式的特点:

- 帧同步信号上降沿时表述一帧数据开始,高电平只维持一个Bit clock宽度,直到下一帧数据开始又变高,同样也是一个Bit clock的宽度。

- 一帧数据除了包含有效的slot,可能还有其它填充数据(Don’t Care)。

- 每帧数据开始传输时,有效数据延迟一个bit clock,即从帧同步信号开始后的第二BICK的上升沿才是第一个有效数据位。

4.5 Mode 4 PCM Long Frame Format

图6 TDM mode PCM Long Frame(TDM256)

如图6,这种传输模式的特点:

- 帧同步信号上降沿时表述一帧数据开始,高电平只维持一个Bit clock宽度,直到下一帧数据开始又变高,同样也是一个Bit clock的宽度。

- 一帧数据除了包含有效的slot,可能还有其它填充数据。

- 每帧数据开始传输时,有效数据位没有延迟

4.6 Mode 5 Irregular I2S Format

图7 TDM mode Irregular I2S Format(TDM256)

如图7,这种传输模式的特点:

- 帧同步信号下降沿时表述一帧数据开始,低电平维持N/2 slot(有效数据的)宽度,再变为高电平,直到下一帧数据开始又变低。

- 每帧数据开始传输时,有效数据延迟一个bit clock,即从帧同步信号开始后的第二BICK的上升沿才是第一个有效数据位。

- 一帧数据除了包含有效的slot,还有其他填充数据。

本文来自互联网用户投稿,文章观点仅代表作者本人,不代表本站立场,不承担相关法律责任。如若转载,请注明出处。 如若内容造成侵权/违法违规/事实不符,请点击【内容举报】进行投诉反馈!