【计算机组成与体系结构Ⅰ】基于Logisim的模型计算机设计

基于Logisim的模型计算机设计

一、实验目的

基于Logisim软件,根据一个模型指令系统,在逐步学习和了解计算机组成各部分逻辑组成和各部分互联的基础上,深入理解课程中的知识点,利用此软件设计并实现一个模拟的8位模型计算机原型。

二、模型计算机指令集和组成

2.1 8位模型计算机的指令系统指令集

- LDA—将数据装入累加器A

- ADD—加法

- SUB—减法

- OUT—输出结果

- HLT—停机

均为单字长、零地址或一地址指令、两个通用R (A ,B)

| 助记符 | 功能 | 指令格式(OP字段) | |

| LDA address | R[Rs]←M[address];Rs:A | 0000 | address |

| ADD address | R[Rs]←M[address]; Rs:B; R[A] ←R[A]+ R[B] | 0001 | address |

| SUB address | R[Rs]←M[address]; Rs:B; R[A] ←R[A]- R[B] | 0010 | address |

| OUT | R[O] ←R[A]; | 1110 | xxxx |

| HLT | 停机 | 1111 | xxxx |

2.2 计算机简化模型的组成(数据通路)

三、实验环境

Logisim-win-2.7.1;

Microsoft Windows 10;

四、实验内容

1:分析指令集指令,结合ppt的第5章第4节内容(ppt补充内容),用Logisim库中的门器件、寄存器、存储器件以及多路选择器、译码器和其他简单的器件来搭建最终的8位模型CPU和模型计算机。

2:将ppt中第5章第4节提供的指令存入存储器,运行结果,并在LED上显示。

3:项目报告:说明每个模块的设计思路,8位模型计算机的测试方法及测试结果。

4:录屏视频:演示利用本作业设计的8位模型计算机运行作业要求的测试汇编代码的结果,利用Led灯或数码管等显示结果。

| 汇编代码如下: LDA 9H ADD AH ADD BH OUT HLT |

五、模块设计

5.1 分析指令集指令

本实验中指令区域的对应关系如下表所示:

| 源程序 | 指令字段 | 存储单元 |

| LDA 9H | 0000 1001 | 0000->R0 |

| ADD AH | 0001 1010 | 0001->R1 |

| ADD BH | 0001 1011 | 0010->R2 |

| OUT | 1110 **** | 0011->R3 |

| HLT | 1111 **** | 0100->R4 |

5.2 分析数据与存储单元

本实验中数据区域的对应关系如下表所示:

| 数据值(十进制) | 数据值(二进制) | 存储单元(地址) |

| 16 | 0001 0000 | 1001->9H |

| 20 | 0001 0100 | 1010->AH |

| 24 | 0001 1000 | 1011->BH |

5.3 设计1位半加器

令A为加数、B为被加数、S为当前位的和、C为当前位的进位,可以得到半加器的真值表如下表所示:

| A | B | S | C |

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

通过真值表,可以得到S和C的逻辑表达式为(其中红色部分为取非结果):

S = AB + AB = A ⊕ B

C = AB + AB

因此,S可以使用异或门求得,C可以使用与门求得。

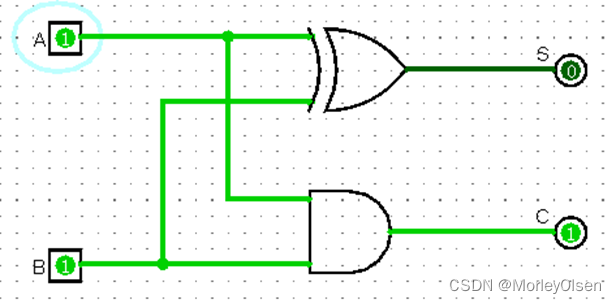

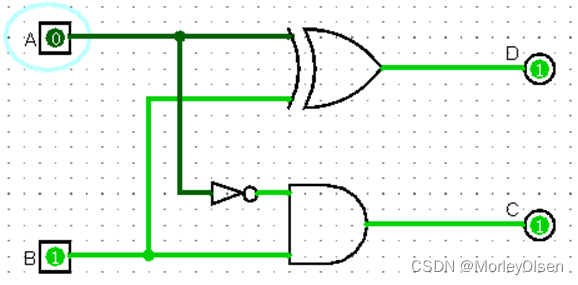

根据上述分析所设计的电路图如下图所示:

经过仿真模拟A、B的值后,发现电路的输出结果与真值表理论分析结果一致,说明电路设计具备正确性。此处以A = 1,B = 1为例进行展示,电路的显示结果如下图所示:

5.4 设计1位全加器

令A为加数、B为被加数、Ci为低位的进位、S为当前位的和、Co为当前位的进位,可以得到全加器的真值表如下表所示:

| Ci | A | B | S | Co |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

通过真值表,可以得到S和Co的逻辑表达式为(其中红色部分为取非结果):

S = ABCi + ABCi + ABCi + ABCi = A ⊕ B ⊕ Ci

Co = ABCi + ABCi + ABCi + ABCi = AB + ACi + BCi

因此,S可以使用异或门求得,Co可以使用与门和或门求得。

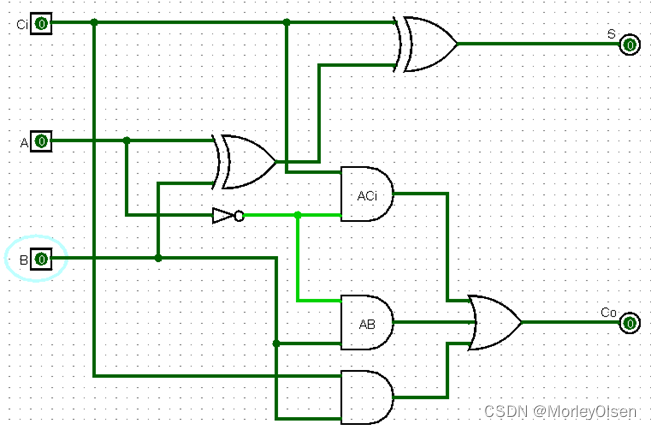

根据上述分析所设计的电路图如下图所示:

经过仿真模拟A、B的值后,发现电路的输出结果与真值表理论分析结果一致,说明电路设计具备正确性。此处以A = 1,B = 1,Ci = 1为例进行展示,电路的显示结果如下图所示:

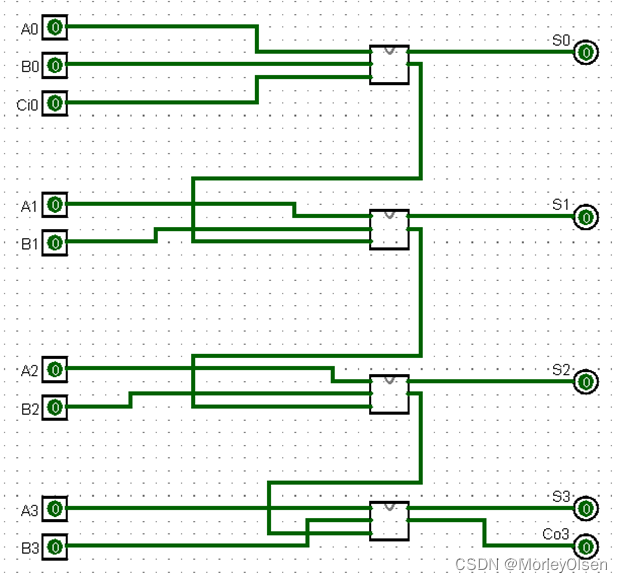

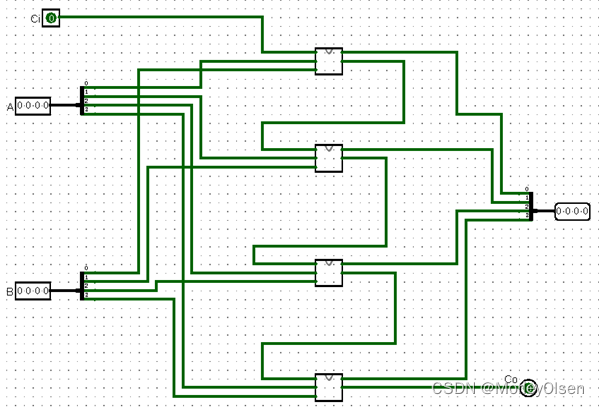

5.5 设计4位全加器

4位全加器可以通过4个1位全加器串行连接组成。通过对1位全加器进行封装后,可以将其作为自设元件插入到电路当中。通过对1位全加器进行接口调整和封装后,其左侧有三个输入端口,从上至下依次是加数、被加数和低位的进位,同时其右侧有两个输出端口,从上至下依次是当前位的和、当前位的进位。最终的封装结果如下图所示:

第一个全加器需要设置加数A0、被加数B0、低位的进位Ci0、当前位的和S0,一共三个输入引脚和一个输出引脚。

由于第二个全加器的低位的进位来源于第一个全加器的当前位的进位,因此不需要额外设置低位的进位的输入引脚。所以,第二个全加器需要设置加数A1、被加数B1、当前位的和S1,一共二个输入引脚和一个输出引脚。

第三个全加器的设置与第二个全加器的设置类似。所以,第三个全加器需要设置加数A2、被加数B2、当前位的和S2,一共二个输入引脚和一个输出引脚。

由于第四个全加器的当前位的进位没有其他元件接收,因此需要额外设置当前位的进位的输出引脚。所以,第四个全加器需要设置加数A3、被加数B3、当前位的和S3、当前位的进位Co3,一共二个输入引脚和二个输出引脚。

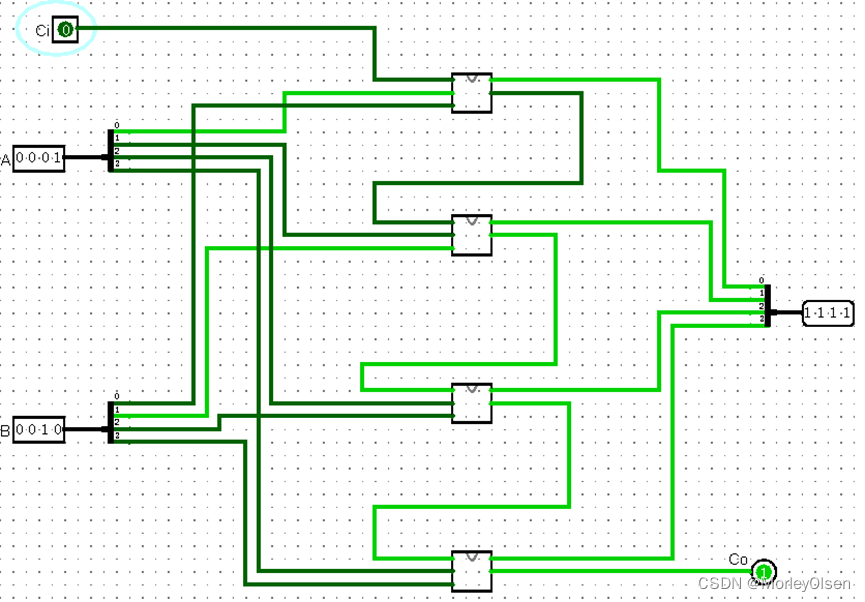

根据上述分析所设计的电路图如下图所示:

经过仿真模拟各输入信号的值后,发现电路的输出结果与理论分析结果一致,说明电路设计具备正确性。此处以A = 1111,B = 1000,Cio = 0为例进行展示,电路的显示结果如下图所示:

5.6 设计8位全加器

8位全加器可以通过2个4位全加器串行连接组成。通过对4位全加器进行封装后,可以将其作为自设元件插入到电路当中。通过对4位全加器进行接口调整和封装后,其左侧有九个输入端口,从上至下依次是加数的第一位值、被加数的第一位值、整体上低位的进位、加数的第二位值、被加数的第二位值、加数的第三位值、被加数的第三位值、加数的第四位值、被加数的第四位值,同时其右侧有五个输出端口,从上至下依次是第一位的和、第二位的和、第三位的和、第四位的和、整体上当前四位的进位。最终的封装结果如下图所示:

第一个4位全加器需要设置加数A的低位四位(即A0至A3)、被加数B的低位四位(即B0至B3)、低位四位的低位的进位Ci、低位四位的当前位的和(即S0至S3),一共九个输入引脚和四个输出引脚。

由于第二个4位全加器的低位的进位来源于第一个4位全加器的当前位的进位,因此不需要额外设置低位的进位的输入引脚。所以,第二个4位全加器需要设置加数A的高位四位(即A4至A7)、被加数B的高位四位(即B4至B7)、高位四位的当前位的和(即S0至S4)、高位四位的当前位的进位Co,一共八个输入引脚和五个输出引脚。

根据上述分析所设计的电路图如下图所示:

经过仿真模拟各输入信号的值后,发现电路的输出结果与理论分析结果一致,说明电路设计具备正确性。此处以A = 1111 1111,B = 1000 0000,Ci = 0为例进行展示,电路的显示结果如下图所示:

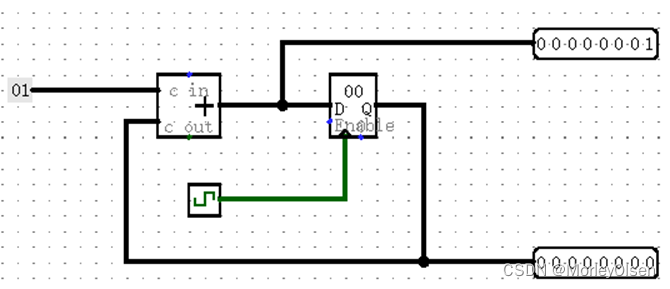

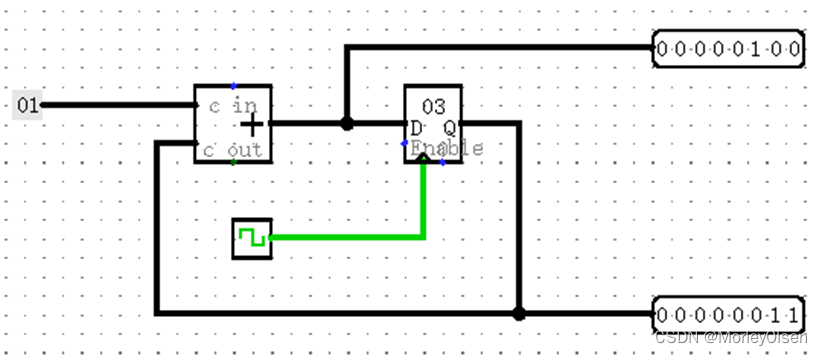

5.7 设计循环累加器

选择位宽均为8的加法器、寄存器、常量、输出引脚作为循环累加器的基本元件,同时加上时钟作为时序控制信号的发生器。将时钟和的寄存器的使能端相连接,来控制寄存器的时序逻辑。寄存器的Q端为当前寄存器的值,D端为当触发时钟端时输入到寄存器的值。加法器的加数固定为0000 0001,被加数固定为寄存器的值,因此被加数端需要连接寄存器的Q端,和端需要连接寄存器的D端。

根据上述分析所设计的电路图如下图所示:

经过仿真模拟各输入信号的值后,发现电路的输出结果与理论分析结果一致,说明电路设计具备正确性。此处以经过三个上升沿为例进行展示,电路的显示结果如下图所示:

5.8 设计半减器

令A为被减数、B为减数、D为当前位的差、C为当前位的借位,可以得到半加器的真值表如下表所示:

| A | B | D | C |

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

通过真值表,可以得到D和C的逻辑表达式为(其中红色部分为取非结果):

D = AB + AB = A ⊕ B

C = AB

因此,D可以使用异或门求得,C可以使用与门和非门求得。根据上述分析所设计的电路图如下图所示:

经过仿真模拟A、B的值后,发现电路的输出结果与真值表理论分析结果一致,说明电路设计具备正确性。此处以A = 0,B = 1为例进行展示,电路的显示结果如下图所示:

5.9 设计1位全减器

令A为被减数、B为减数、Ci为高位的借位、D为当前位的差、Co为当前位的借位,可以得到全加器的真值表如下表所示:

| Ci | A | B | D | Co |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 0 |

| 1 | 0 | 0 | 1 | 1 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 |

通过真值表,可以得到S和Co的逻辑表达式为(其中红色部分为取非结果):

D = ABCi + ABCi + ABCi + ABCi = A ⊕ B ⊕ Ci

Co = ABCi + ABCi + ABCi + ABCi = AB + ACi + BCi

因此,D可以使用异或门求得,Co可以使用与门、非门和或门求得。

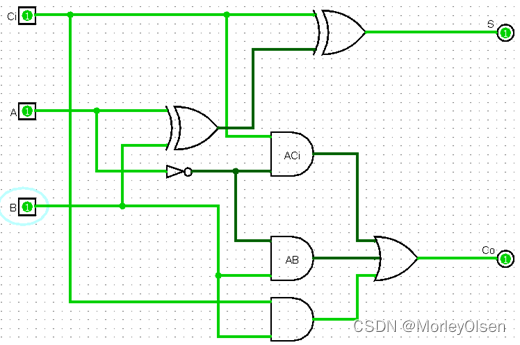

根据上述分析所设计的电路图如下图所示:

经过仿真模拟A、B的值后,发现电路的输出结果与真值表理论分析结果一致,说明电路设计具备正确性。此处以A = 1,B = 1,Ci = 1为例进行展示,电路的显示结果如下图所示:

5.10 设计4位全减器

4位全减器可以通过4个1位全减器串行连接组成。通过对1位全减器进行封装后,可以将其作为自设元件插入到电路当中。通过对1位全减器进行接口调整和封装后,其左侧有三个输入端口,从上至下依次是被减数A、减数B、高位的借位Ci,同时其右侧有两个输出端口,从上至下依次是当前位的差D、当前位的借位Co。最终的封装结果如下图所示:

设置串行连接组成的4位全减器的时候,需要将高位全减器的Co端与低位全减器的Ci端相连接。同时,如果A和B的差值为正数,则输出结果为原码;如果A和B的差值为负数,则输出结果为补码。

根据上述分析所设计的电路图如下图所示:

经过仿真模拟A、B的值后,发现电路的输出结果与真值表理论分析结果一致,说明电路设计具备正确性。此处以A = 0001,B = 0010,Ci = 0为例进行展示,电路的显示结果如下图所示:

5.11 设计8位全减器

8位全减器可以通过2个4位全减器串行连接组成。通过对4位全减器进行封装后,可以将其作为自设元件插入到电路当中。通过对4位全减器进行接口调整和封装后,其左侧有三个输入端口,从上至下依次是被减数A的其中四位、减数B的其中四位、高位的借位Ci,同时其右侧有两个输出端口,从上至下依次是当前四位的差D、当前位的借位Co。最终的封装结果如下图所示:

与设计4位全减器时的思路类似,设置串行连接组成的8位全减器的时候,需要将高四位全减器的Co端与低四位全减器的Ci端相连接。同时,如果A和B的差值为正数,则输出结果为原码;如果A和B的差值为负数,则输出结果为补码。

根据上述分析所设计的电路图如下图所示:

经过仿真模拟A、B的值后,发现电路的输出结果与真值表理论分析结果一致,说明电路设计具备正确性。此处以A = 0000 0000,B = 0000 0001,Ci = 0为例进行展示,电路的显示结果如下图所示:

5.12 设计通用寄存器

在本实验中,需要有两个位宽为8的通用寄存器,分别命名为D1和D2。外部接口需要设置时钟信号Clock、复位信号Reset、数据输入端Input、数据输出端Output、输出使能端Enable等。

(1)设计输出使能控制元件

在本实验中,预设当Enable = 1时,允许读出寄存器中的数据;当Enable = 0时,不允许读出寄存器中的数据,默认输出空值0000 0000。因此,需要将输出使能信号与数据各位进行取【与】的操作,即将使能信号与数据各位同时通过与门进行判断。

根据上述分析所设计的电路图如下图所示:

经过仿真模拟A的值后,发现电路的输出结果与真值表理论分析结果一致,说明电路设计具备正确性。此处以A = 0000 0011,enable = 1为例进行展示,电路的显示结果如下图所示:

(2)设计寄存器模块

在本实验中,通过两个数据输入端A、B分别对D2和D1寄存器进行写入操作,时钟信号来临时即写入两个数据输入端的数据进寄存器,复位信号来临时即清空两个寄存器内的数据。输出使能端通过控制输出使能控制元件来控制D2寄存器的数据的读取,与(1)处的设计一致。

通过对输出使能控制元件进行接口调整和封装后,其左侧有二个输入端口,从上至下依次是数据输入端、enable端,同时其右侧有一个输出端口,即数据输出端。最终的封装结果如下图所示:

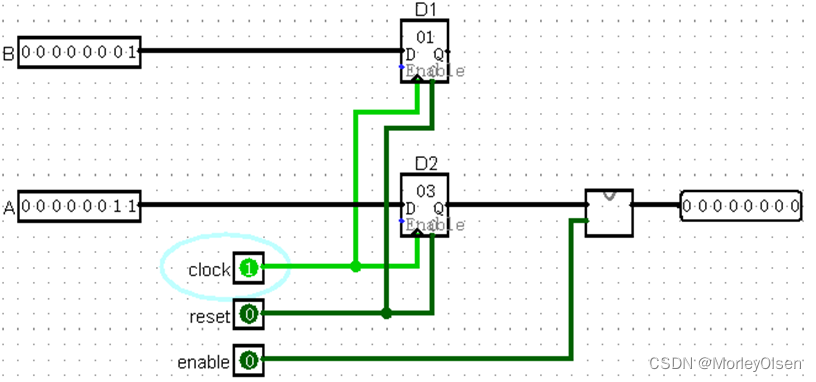

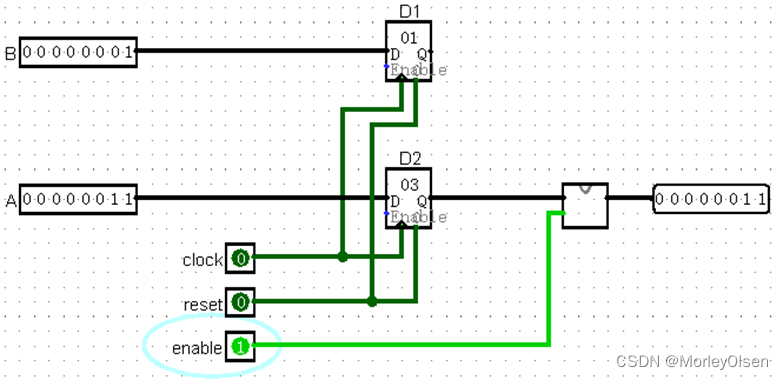

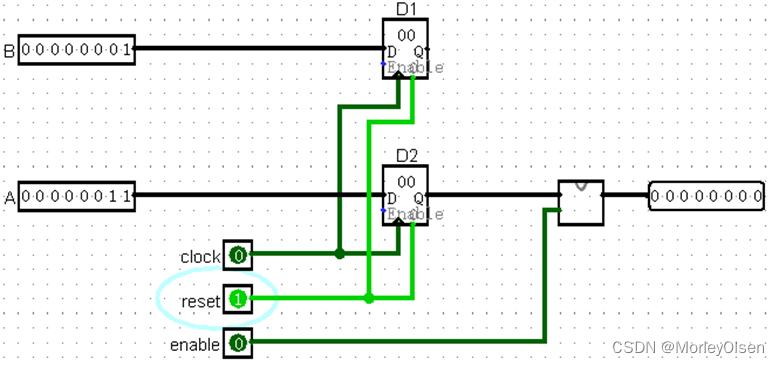

根据上述分析所设计的电路图如下图所示:

为了说明电路设计具备正确性,此处以A = 0000 0011,B = 0000 0001为例依次进行写入、读取、重置的操作展示,电路的显示结果如下图所示:

写入:

读取:

重置:

5.13 设计ALU

(1)ALU的简介

ALU,即算术逻辑运算单元。ALU 的主要功能是对输入到ALU的两个数进行加法、减法等操作。ALU 内部包括8位加法器、减法器等部件。

ALU的模块接口如下表所示:

| 信号 | 方向 | 描述 |

| A | 输入 | 参与ALU运算的第一个值,来自寄存器A |

| B | 输入 | 参与ALU运算的第二个值,来自寄存器B |

| EU | 输入 | ALU进行加法运算 |

| SU | 输入 | ALU进行减法运算 |

| Result | 输出 | ALU计算的结果 |

(2)设计ALU各模块

根据ALU的运算控制表可知,ALU中需要设计输入选择器、8位逻辑或运算、8位逻辑与运算、8位加法运算、8位减法运算等部件。

(3)设计8位逻辑或运算

8位逻辑或运算,只需要将A和B的每一位分别做或运算后,再合并成Z进行输出即可。

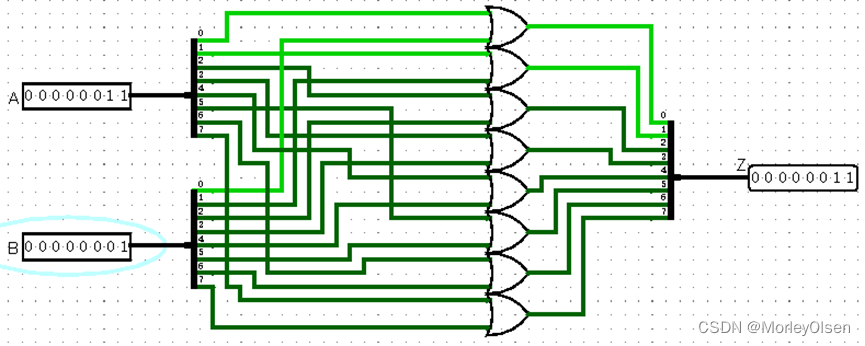

根据上述分析所设计的电路图如下图所示:

为了说明电路设计具备正确性,此处以A = 0000 0011,B = 0000 0001为例进行展示,电路的显示结果如下图所示:

(4)设计8位补码转换器

由于可以通过原码转补码的操作来运行减法运算,因此在此处设计8位补码转换器来辅助ALU的运算功能的实现。负数的补码为符号位不变,其余部分取反加1。根据此性质,可以先对输入数据的每一位与1做异或操作,执行取反的部分,再通过8位加法器加上1,即可得到补码。

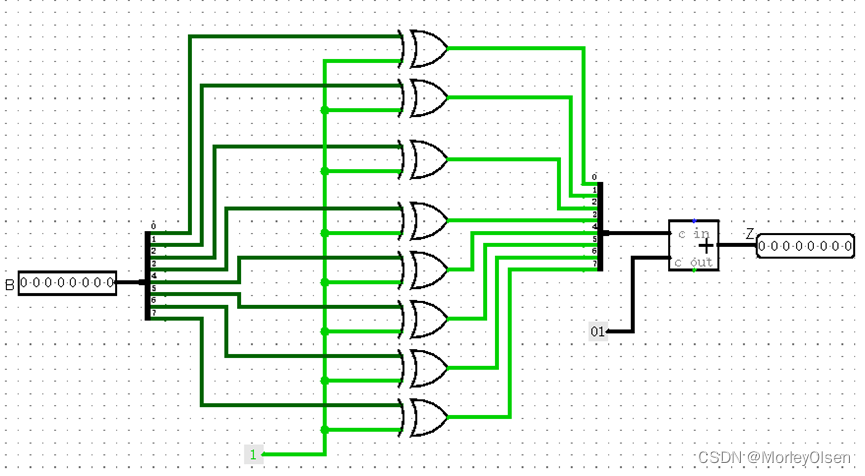

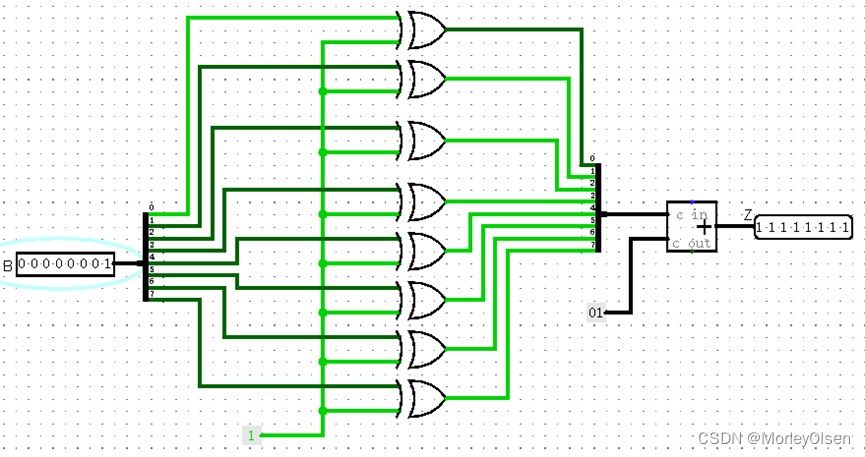

根据上述分析所设计的电路图如下图所示:

为了说明电路设计具备正确性,此处以B = 0000 0001为例进行展示,电路的显示结果如下图所示:

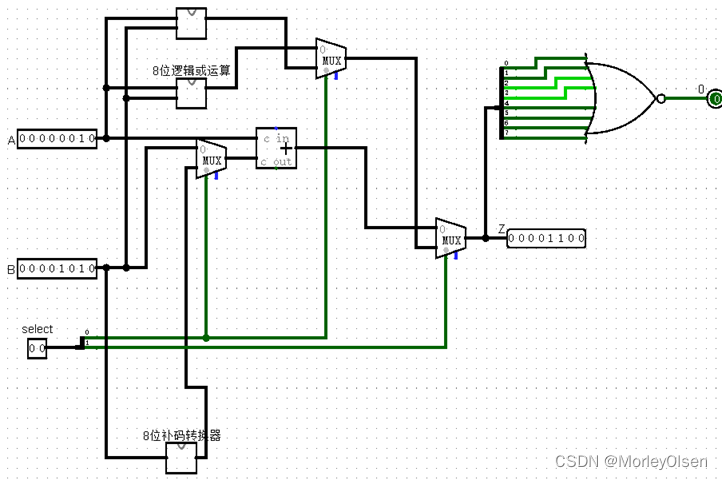

(5)组装为ALU

通过功能选择端的数值,控制S1和S0的数值,再让其通过数据选择器进行筛选,从而选择ALU执行的运算功能。当选择减法运算时,通过8位补码转换器,将减法变更为加法运算。同时,在输出端增加一个判断输出是否为0的部件,以便更好地展示ALU的输出数值。

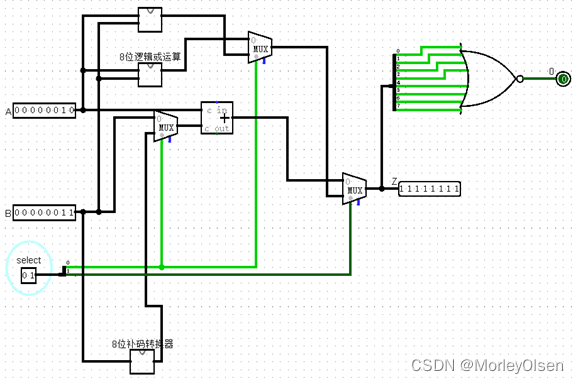

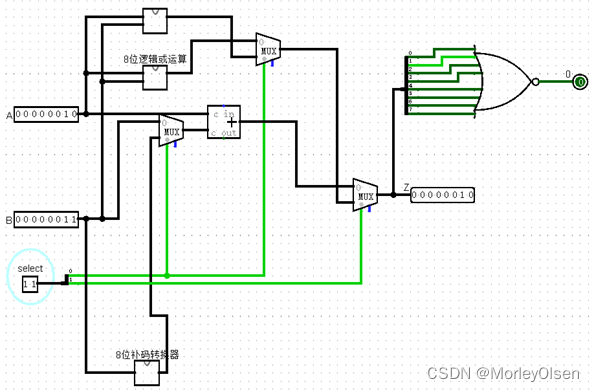

根据上述分析所设计的电路图如下图所示:

令S0、S1为ALU的输入选择端,通过控制S0和S1的值即可控制ALU的运算模式,其运算控制表如下表所示:

| S1 | S0 | ALU运算 |

| 0 | 0 | A 加 B |

| 0 | 1 | A 减 B |

| 1 | 0 | A 或 B |

| 1 | 1 | A 与 B |

为了说明电路设计具备正确性,此处依次进行ALU中加法、减法、或、与运算的展示,电路的显示结果如下图所示:

加法:

S1 = 0,S2 = 0,令A = 0000 0001,B = 0000 0011.

减法:

S1 = 0,S2 = 1,令A = 0000 0001,B = 0000 0011.

或:

S1 = 1,S2 = 0,令A = 0000 0001,B = 0000 0011

与:

S1 = 1,S2 = 0,令A = 0000 0001,B = 0000 0011

5.14 设计控制器

控制器是CPU的核心部件,其可以通过设置不同的值来控制各项功能的操作。在本实验中,需要设计两个解复用器、两个ALU选择控制端、一个时钟信号控制端,共计五个控制端口。

控制器需要生成对CPU 中数据通路进行控制的控制信号,即取指、译码、取数、运算、输出结果等功能。在本实验中,指令与其所对应的OP字段如下表所示:

| 指令 | OP字段 |

| LDA 9H | 0000 1001 |

| ADD AH | 0001 1010 |

| ADD BH | 0001 1011 |

| OUT | 1110 **** |

| HLT | 1111 **** |

通过各个控制端口的真值表,可以获得其逻辑表达式,从而方便使用基本的门电路进行搭建。令高四位分别位S4、S3、S2、S1,则可以得出各个控制端口的逻辑表达式为(其中红色部分为取非结果):

ALU选择控制端1 = S2 + S3

ALU选择控制端2 = S3

解复用器控制端1 = S4

解复用器控制端2 = S4 + S3 + S2

时钟信号控制端 = S4 + S3 + S2 + S1

根据上述分析所设计的电路图如下图所示:

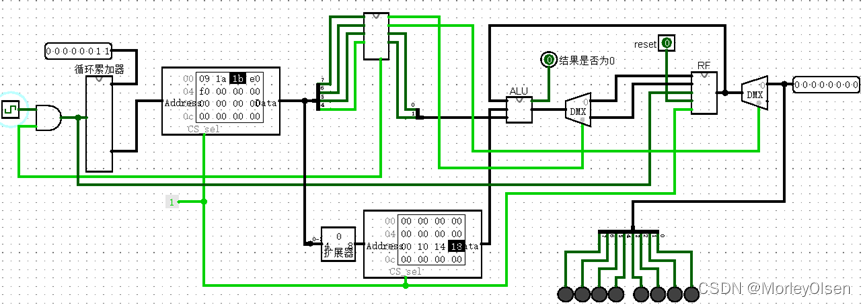

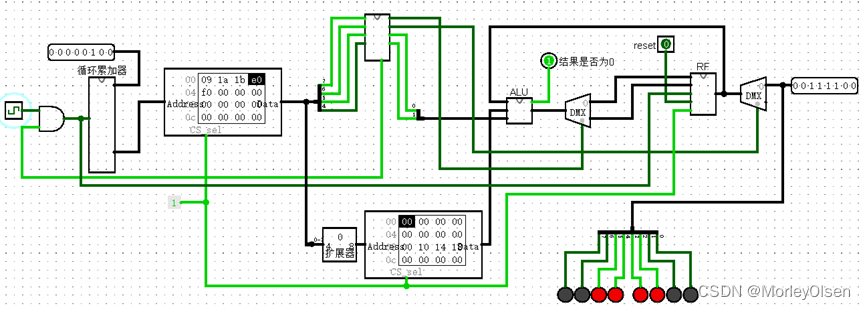

5.15 设计基于自设元件所组装的CPU

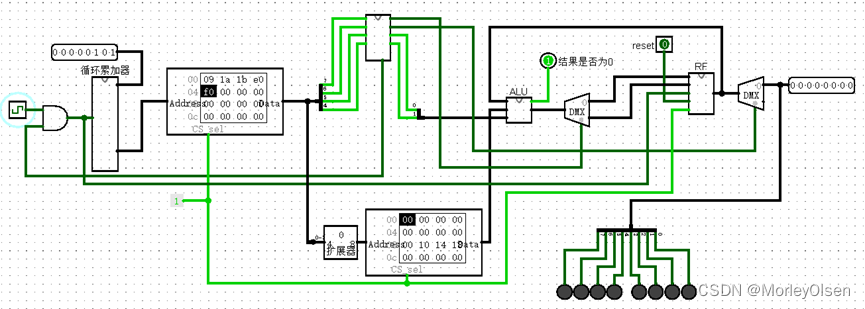

CPU 受时钟信号的控制循环地执行指令,且由数据通路和控制器组成。数据通路中包含组合逻辑单元和状态单元。其中,组合逻辑单元用于对数据进行处理,包括ALU、位扩展器、数据选择器等;状态单元由寄存器RF和2个只读存储器 ROM 组成。在本实验中,数据通路为非总线式单周期数据通路。CPU通过给 ROM 中预置指令来达到预期的工作效果。CPU的输入端为时钟信号,输出端为八个发光二极管和一个8位的输出引脚。

根据上述分析所设计的电路图如下图所示:

六、8位模型计算机的测试

(1)理论分析

本实验中时序情况下的指令与地址的对应关系如下表所示:

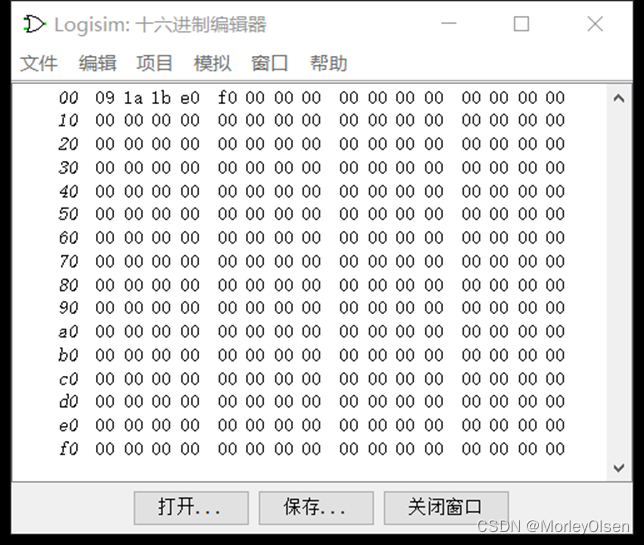

| 源程序 | 指令字段 | ROM预置 |

| LDA 9H | 0000 1001 | 09 H |

| ADD AH | 0001 1010 | 1A H |

| ADD BH | 0001 1011 | 1B H |

| OUT | 1110 0000 | E0 H |

| HLT | 1111 0000 | F0 H |

| / | 0000 0000 | 00 H |

数据在不同进制下的对应关系如下表所示:

| 数据(十进制) | 二进制 | 十六进制 |

| 16->09 H地址的数据 | 0001 0000 | 10 H |

| 20->1A H地址的数据 | 0001 0100 | 14 H |

| 24->1B H地址的数据 | 0001 1000 | 18 H |

分析源程序可知,最终的计算结果为16 + 20 + 24 = 60 = 0011 1100 H.

(2)实际测试

1:加载09H单元的数据。

2:加上1A单元的数据。

3:加上1B单元的数据。

4:输出运算结果。

5:停机。

七、实验心得

在本次实验中,从一开始一股脑子地逐个设计全减器和全加器,到发现能够使用Logisim自带的加法器,再到设计循环累加器实现在实验课中所遇到的AR1_INC的自增功能,再到结合实验课中的ALU的特性设计通用寄存器等元件,我不断地对所设计的CPU进行优化和改进工作,最终实现了一款简易的8位模型计算机。

所建的所有电路或集成元件如下图所示:

俗话说:实践出真知。我虽然在本次实验中花费了较多的时间和精力(特别是在考试月内逐步实现各个部分的功能),但是对计算机组成原理有了更加深刻的认识和理解,也算是一种痛并快乐着的生活吧。

八、其他琐碎的经验杂谈

本部分将补充使用Logisim的一些与技巧,进行一定的归纳总结工作。

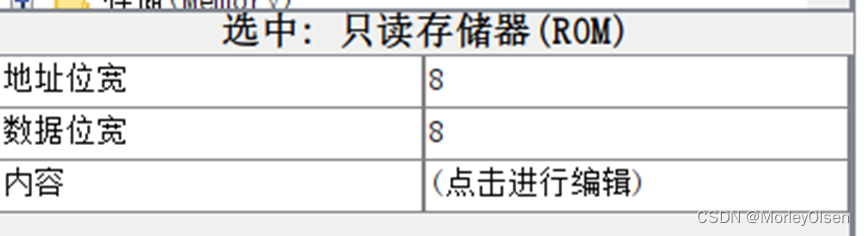

8.1 ROM的内存设置

第一步:点击只读存储器ROM。

第二步:在左下角处点击【内容】,进行内存的编辑。

第三步:点击需要修改的存储单元,依次输入高位和低位的信息,并注意该存储单元为16进制表示的。

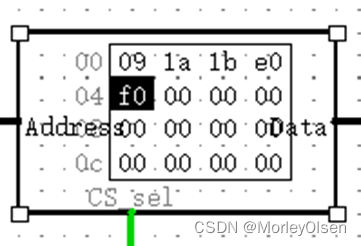

第四步:修改完成后,点击关闭窗口即可。

第五步:观察到电路中的ROM内存已经被修改,表示操作完毕。

8.2 编辑集成后的电路外观

第一步:右键点击所需要集成的元件。

第二步:点击【编辑电路外观】。

第三步:拖拽边框、端口、曲线等外观至理想状态。同时,长按端口时,在右下角会出现对应的端口在电路中的位置。

第四步:点击ctrl+s,进行保存。

8.3 在新电路中添加集成元件

第一步:点击目标的集成元件。

第二步:左键保持按下状态,拖拽到新电路中的预设位置。

本文来自互联网用户投稿,文章观点仅代表作者本人,不代表本站立场,不承担相关法律责任。如若转载,请注明出处。 如若内容造成侵权/违法违规/事实不符,请点击【内容举报】进行投诉反馈!