华中科技大学 计算机组成原理 educoder Logisim平台 存储系统设计

目录

- 实验目的:

- 第1关:汉字字库存储芯片扩展实验

- 第2关:MIPS寄存器文件设计

- 第3关:MIPS RAM设计

- 第4关:全相联cache设计

- 第5关:直接相联cache设计

- 第6关:4路组相连cache设计

- 第7关:2路组相联cache设计

- 测试结果:

实验目的:

1、理解计算机中的重要部件:存储器。

2、学习存储扩展的基本方法,能利用所学理论知识进行设计 MIPS 寄存器堆、MIPS RAM 存储器。

3、能够利用所学习的 cache 的基本原理设计直接相联、全相联,组相联映射的硬件 cache。

第1关:汉字字库存储芯片扩展实验

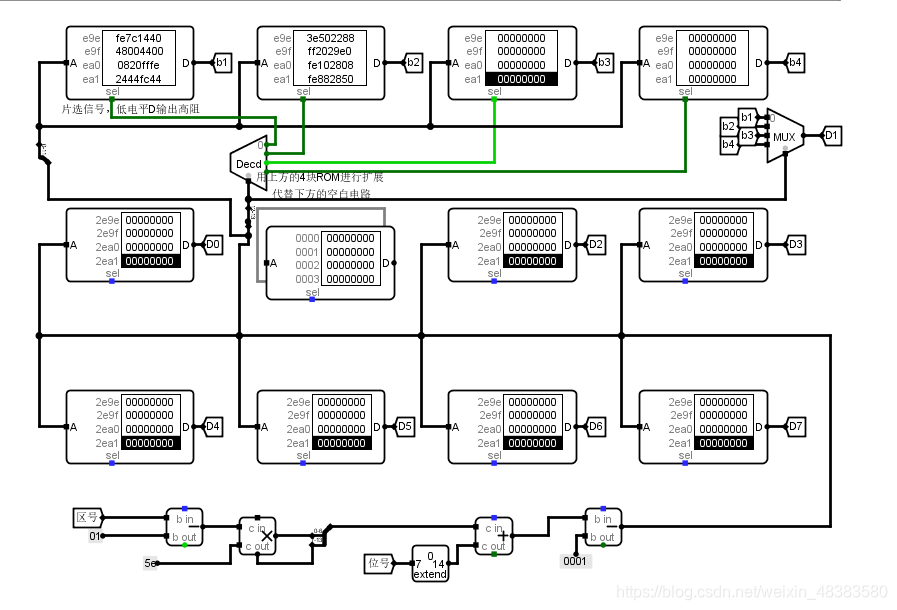

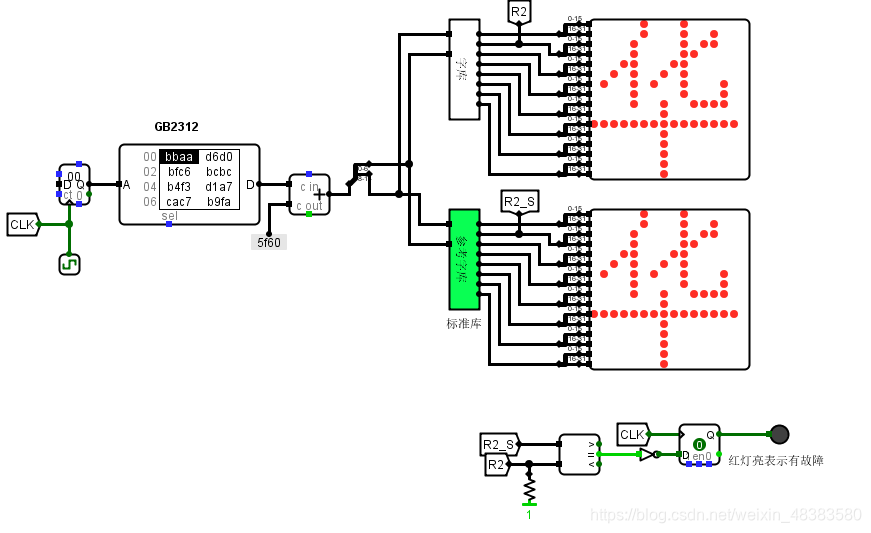

汉字点阵为1616位。需要8片16K32位ROM来存储点阵信息。我们需要用4片4K32位ROM代替其中一片16K32位ROM。4K需要12根地址线,16K需要14根地址线。所以高位多余的两位作为片选信号。我们需要一个数据选择器,来进行选择输出那一片ROM中的数据。再根据数据进行分析,数据的最后两位是选片区的。所以将最后两位直接输入到选择器选择短。最后将数据对应连接,及可得到电路。

第2关:MIPS寄存器文件设计

MIPS拥有32个通用寄存器,一个pc寄存器,一个HI和LO寄存器,另外协处理器也有自己的寄存器,如CP0有32个单独的寄存器,浮点协处理单元也有自己独立的寄存器。

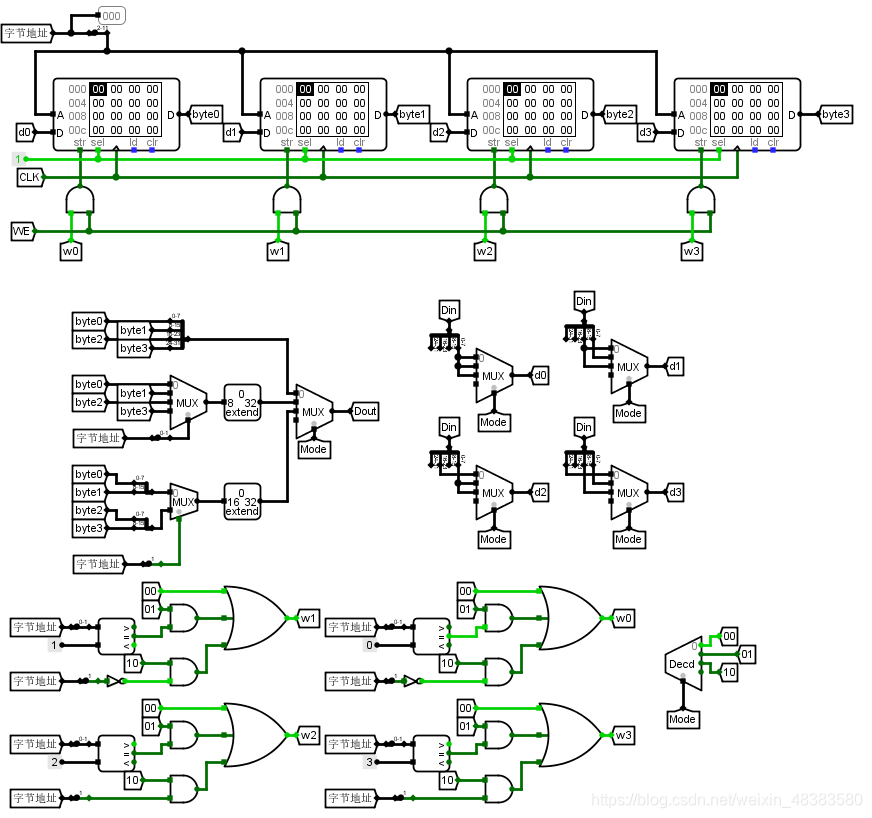

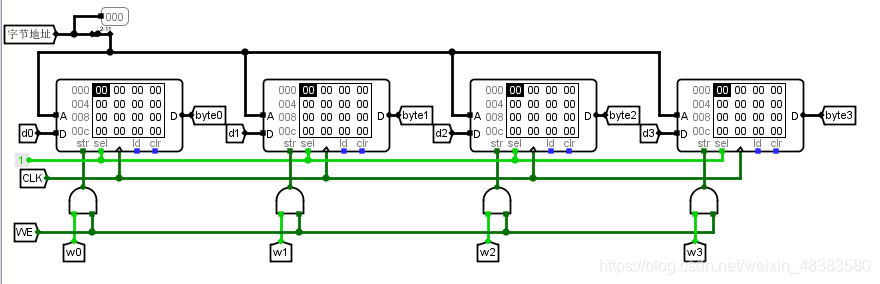

第3关:MIPS RAM设计

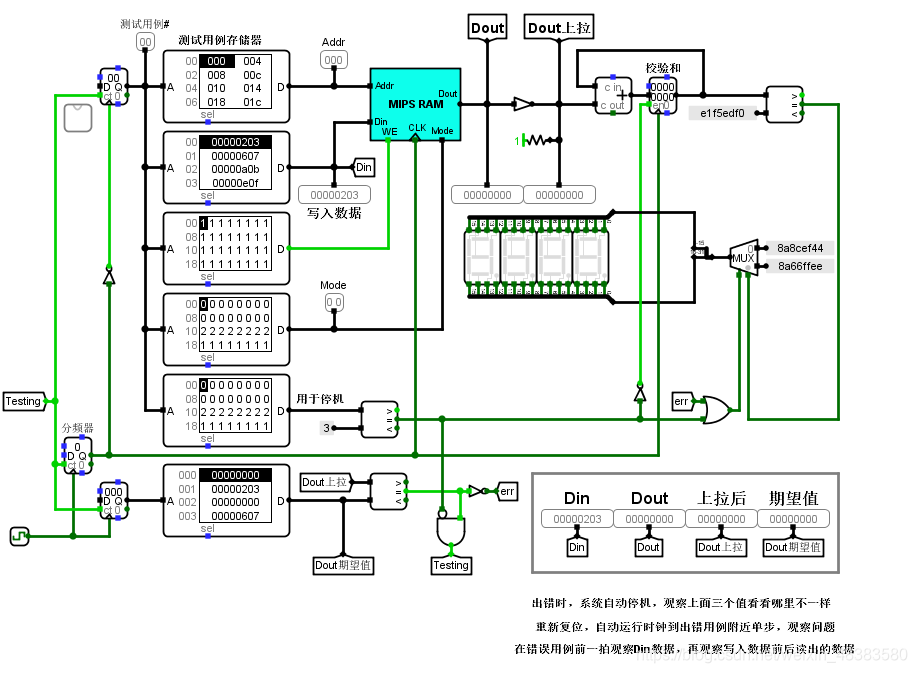

Logisim 中 RAM 组件只能提供固定的地址位宽,数据输出也只能提供固定的数据位宽,访问时无法同时支持字节/半字/字三种访问模式,实验要求利用4个8位的 RAM 组件进行扩展,设计完成既能按照8位、也能按16位、也能按照32位进行读写访问的32位存储器,最终存储器引脚定义如下图。

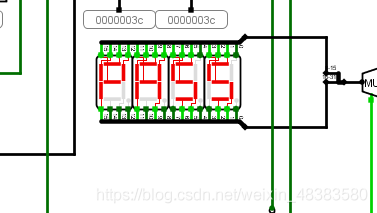

按Ctrl+K启动后,可以看到PASS

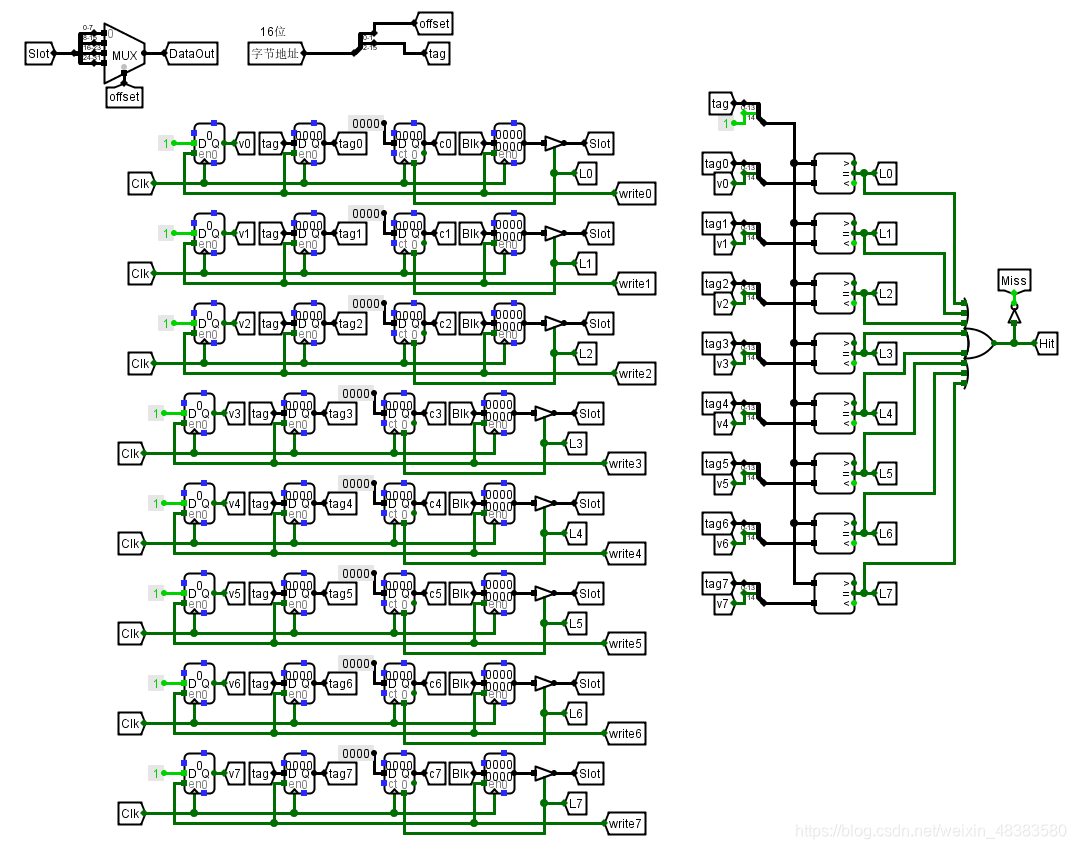

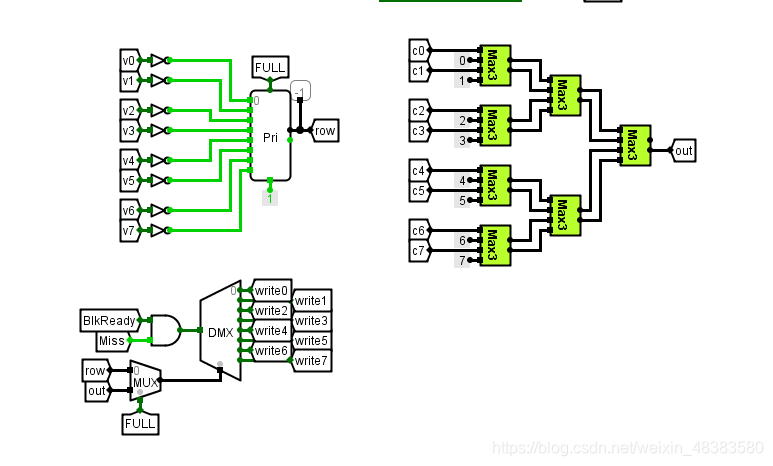

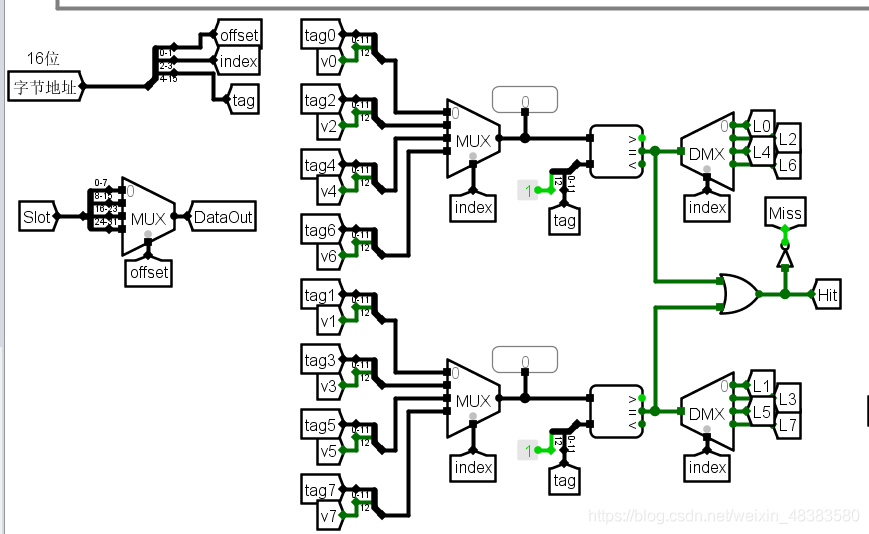

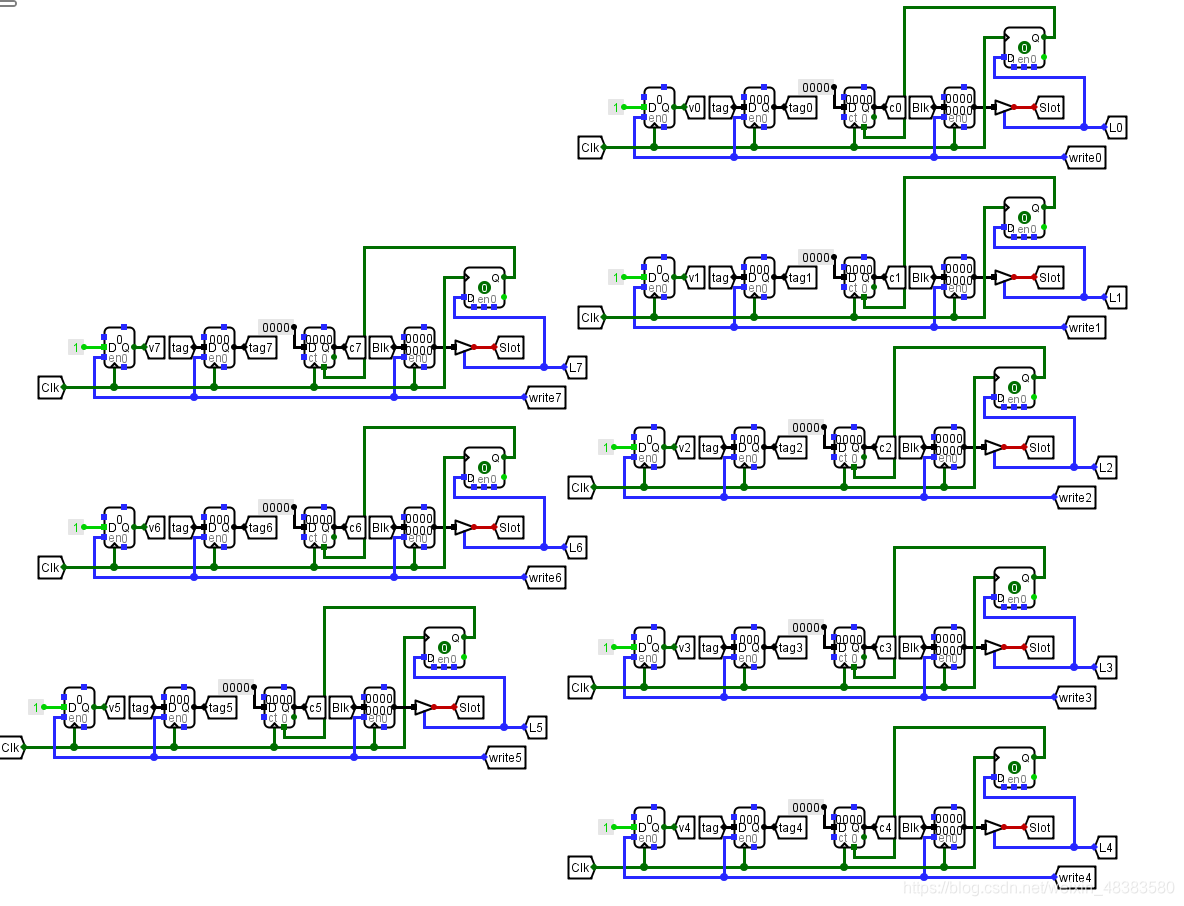

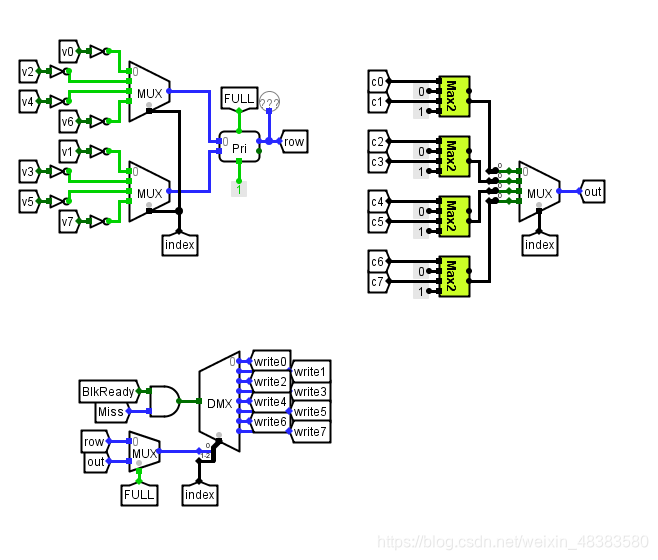

第4关:全相联cache设计

学生掌握 cache 实现的三个关键技术:数据查找,地址映射,替换算法,熟悉译码器,多路选择器,寄存器的使用,能根据不同的映射策略在 Logisim 平台中用数字逻辑电路实现 cache 机制。

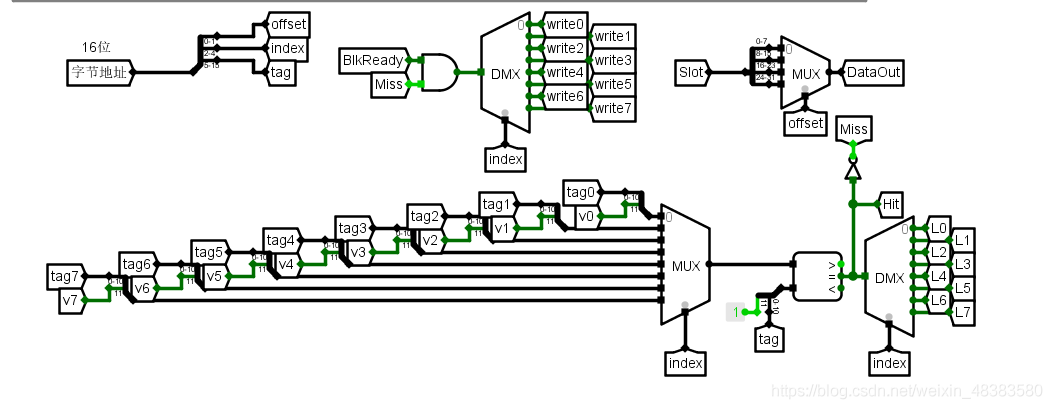

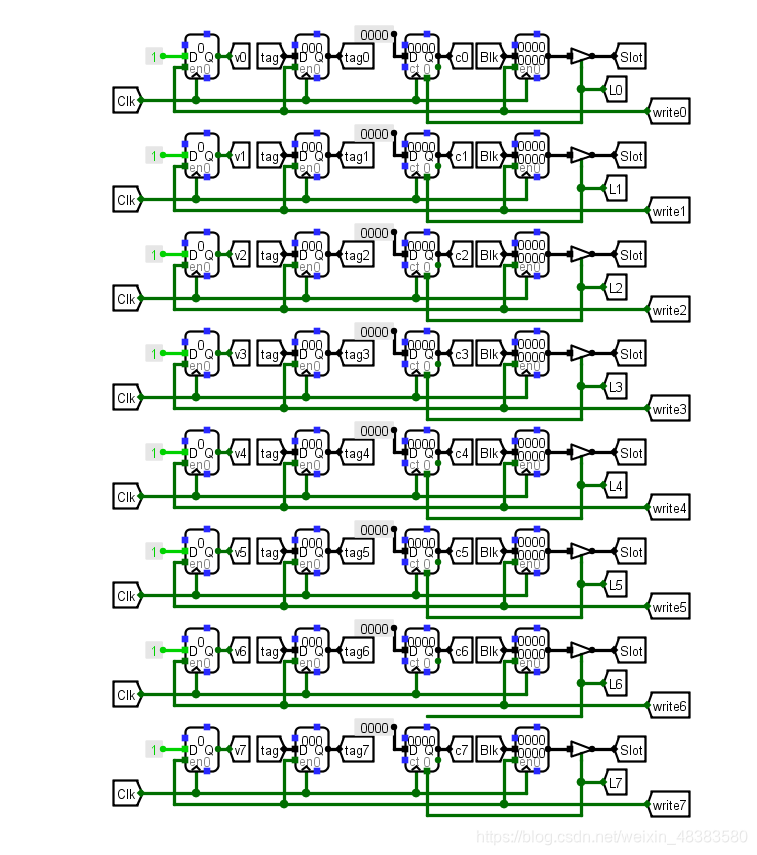

第5关:直接相联cache设计

第6关:4路组相连cache设计

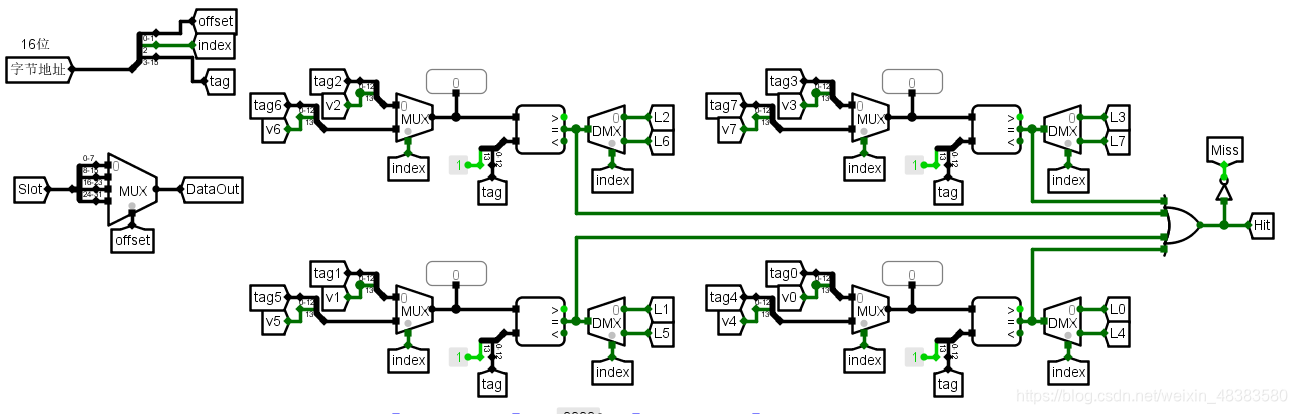

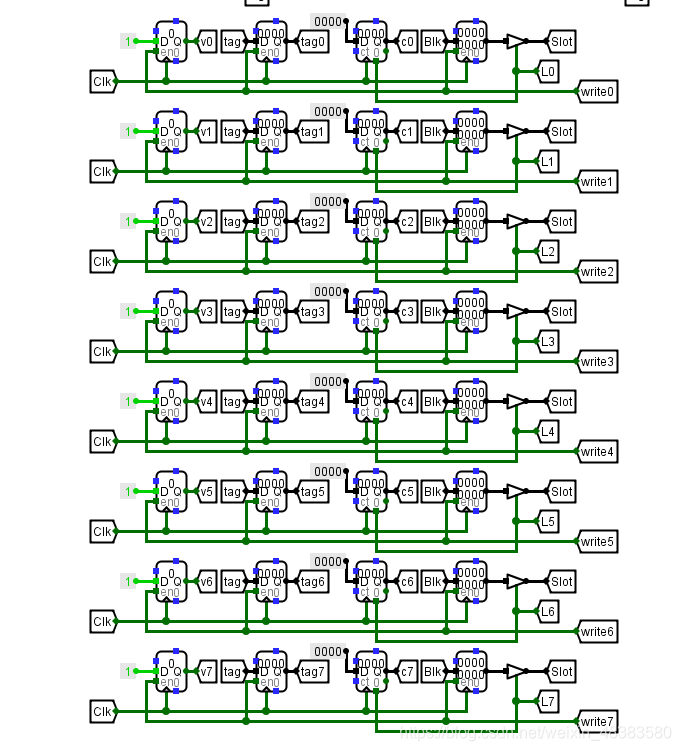

第7关:2路组相联cache设计

测试结果:

本文来自互联网用户投稿,文章观点仅代表作者本人,不代表本站立场,不承担相关法律责任。如若转载,请注明出处。 如若内容造成侵权/违法违规/事实不符,请点击【内容举报】进行投诉反馈!