Quartus II报错

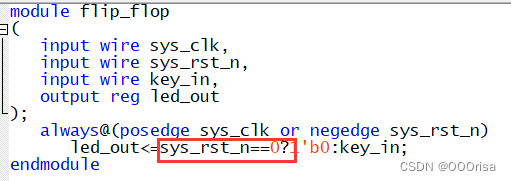

使用如下电路语句创建异步时序实现D触发器时

一直报错

Error (10200): Verilog HDL Conditional Statement error at flip_flop.v(9): cannot match operand(s) in the condition to the corresponding edges in the enclosing event control of the always construct

在网上查了好久都是说要加上if(!sys_rst_n),但我不想采用if语句判断,不明所以然。后来明白,由于敏感事件表中是对复位信号的下降沿敏感,而在always语句中进行判断时使用的是sys_rst_n是否为1,产生矛盾,无法进行综合。

将代码更改如下,可正常运行,前面所述增加if(!sys_rst_n)本质也是一样

参考文章:(51条消息) error10200(转载)_Mr5的博客-CSDN博客

本文来自互联网用户投稿,文章观点仅代表作者本人,不代表本站立场,不承担相关法律责任。如若转载,请注明出处。 如若内容造成侵权/违法违规/事实不符,请点击【内容举报】进行投诉反馈!